# Embedded Testing Architectures

# DISSERTATION

submitted to the Inquiry Commission, designated by the General Assembly of Special Composition of the Department of Computer Science & Engineering of the School of Sciences of University of Ioannina,

by

Vasileios Tenentes

in partial fulfillment of the requirements

FOR THE DEGREE OF DOCTOR OF PHILOSOPHY

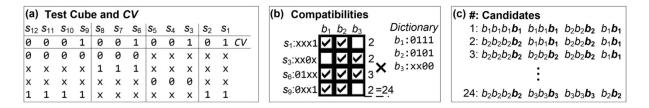

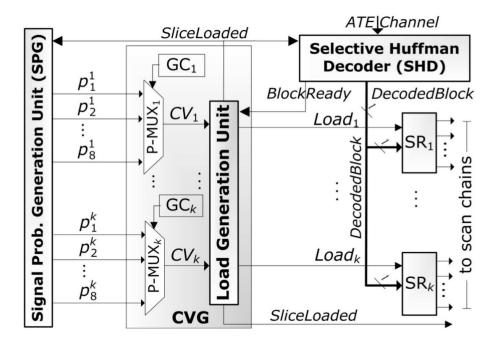

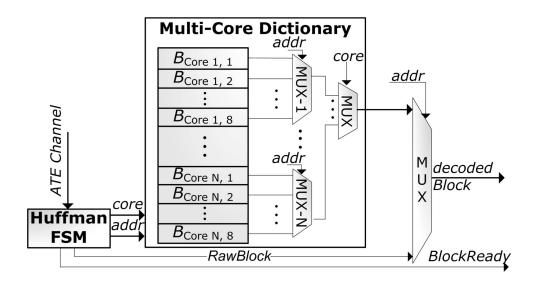

June 2013

#### Advisory Committee

Xrysovalantis Kavousianos University of Ioannina

Yiorgos Tsiatouhas University of Ioannina

Krishnendu Chakrabarty Duke University

#### Inquiry Commission

Xrysovalantis Kavousianos University of Ioannina

Yiorgos Tsiatouhas University of Ioannina

Krishnendu Chakrabarty Duke University

Aristides Efthymiou University of Ioannina

Dimitris Nikolos University of Patras

Dimitris Gizopoulos University of Athens

Emmanouil Kalligeros University of the Aegean ©Copyright by Vasileios Tenentes 2013 All Rights Reserved This thesis is deticated to my parents. For their endless love, support and understanding

# Acknowledgements

First and foremost I have to thank my *parents* for their love and support throughout my life.

I would like to sincerely thank my supervisor, *Prof. Kavousianos*, for his guidance and support throughout this study, and especially for his confidence in me. I wish that the priviledge of working closely with him blessed me with just some of his virtues as a scientist and a person. I would also like to thank *Prof. Chakrabarty* for serving as a member of my thesis committee and for the oportunity he gave me to spend some months at Duke University. Not just his insight and his ingenious mind, but also his multicultural personality make the work with him a delightful experience. Also, I thank *Prof. Tsiatouhas* for the discussions we had and his important tutoring and *Prof. Kalligeros* for the interpretation of some results presented in this thesis.

Also, I want to thank my colleagues Vartziotis and Sfikas for the important discussions we had throughout many lunches.

To all my *friends*, thank you for your understanding and encouragement. Although, I cannot list your names, you are always part of my life.

I am also grateful to all those people that supported with their hard work the "Heraclitus II" scholarships.

# TABLE OF CONTENTS

| 1        | Intr | oducti | on 1                                                                                                                       |

|----------|------|--------|----------------------------------------------------------------------------------------------------------------------------|

|          | 1.1  | Prolog | gue                                                                                                                        |

|          | 1.2  | Manuf  | Cacturing of Integrated Circuits                                                                                           |

|          | 1.3  | Defect | s' Sources                                                                                                                 |

|          | 1.4  | Manuf  | Cacturing Testing                                                                                                          |

|          | 1.5  | Struct | ural Manufacturing Testing                                                                                                 |

|          | 1.6  | Model  | ing of Unmodeled Defects                                                                                                   |

|          | 1.7  | Basic  | Test Cost Factors    9                                                                                                     |

|          | 1.8  | Desigr | for Testability $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $10$                               |

|          |      | 1.8.1  | Ad-hoc DFT                                                                                                                 |

|          |      | 1.8.2  | Scan Design                                                                                                                |

|          |      | 1.8.3  | Built-In Self-Test                                                                                                         |

|          |      | 1.8.4  | Test Resource Partitioning                                                                                                 |

|          | 1.9  | Additi | onal Test Challenges                                                                                                       |

|          |      | 1.9.1  | The post-Dennard Era: Low-power Testing                                                                                    |

|          |      | 1.9.2  | Multi-Core Systems-on-Chips and IP Cores                                                                                   |

|          | 1.10 | Contri | butions & Dissertation Structure                                                                                           |

| <b>2</b> | Bac  | kgroui | d 21                                                                                                                       |

|          | 2.1  | -      | $Models \dots \dots$ |

|          |      | 2.1.1  | Stuck-at Faults                                                                                                            |

|          |      | 2.1.2  | Transistor Faults: Stuck-open and Stuck-short                                                                              |

|          |      | 2.1.3  | Wire Open and Short Faults                                                                                                 |

|          |      | 2.1.4  | Delay testing and Delay Fault Models                                                                                       |

|          |      | 2.1.5  | Automatic Test Pattern Generation                                                                                          |

|          |      | 2.1.6  | N-detection                                                                                                                |

|          |      | 2.1.7  | Unmodeled Faults                                                                                                           |

|          | 2.2  | Test F | Response Partitioning Techniques                                                                                           |

|          |      | 2.2.1  | Static LFSR Reseeding Techniques                                                                                           |

|          |      | 2.2.2  | Dynamic LFSR Reseeding                                                                                                     |

|          |      | 2.2.3  | Code-based Techniques                                                                                                      |

|          |      | 2.2.4  | Industry Practice: Embedded Deterministic Test (EDT) 39                                                                    |

|          | 2.3  | Low-Power Testing Techniques                                  | 41 |

|----------|------|---------------------------------------------------------------|----|

|          |      | 2.3.1 Structural Low-Power Testing Approaches                 | 42 |

|          |      | 2.3.2 Algorithmic Approaches: Low-Power X-Filling Techniques  | 44 |

| 3        | Sta  | te-Skip LFSRs: Bridging the Gap between Test Data Compression |    |

|          | and  | Test Set Embedding                                            | 46 |

|          | 3.1  | Overview                                                      | 46 |

|          | 3.2  | Motivation                                                    | 47 |

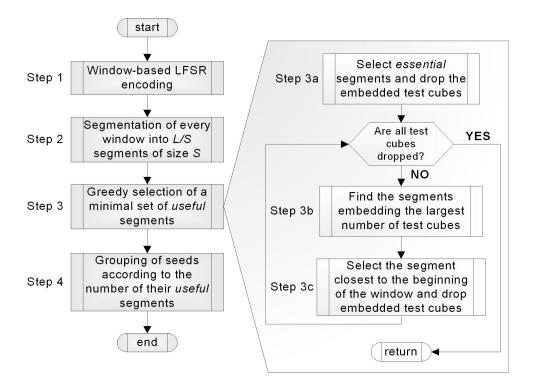

|          | 3.3  | State-Skip Circuit And Proposed LFSR Encoding                 | 49 |

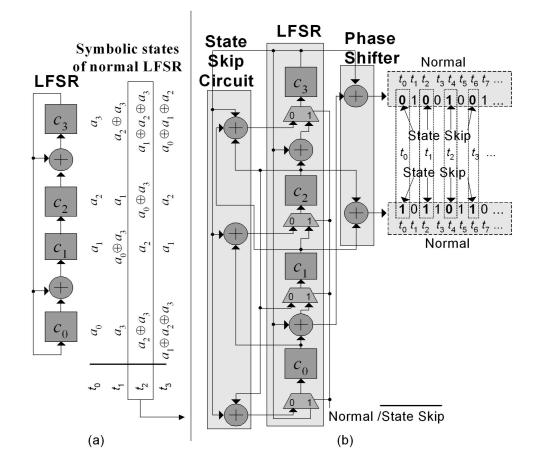

|          |      | 3.3.1 State-Skip Circuit                                      | 50 |

|          |      | 3.3.2 LFSR Encoding using State-Skip Circuits                 | 52 |

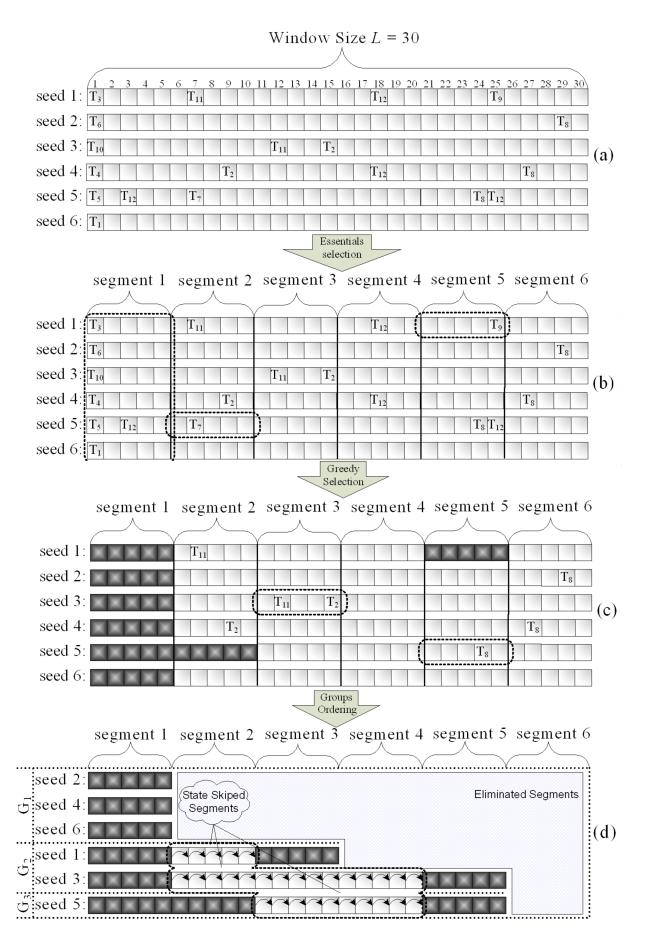

|          | 3.4  | Single-State-Skip LFSRs                                       | 56 |

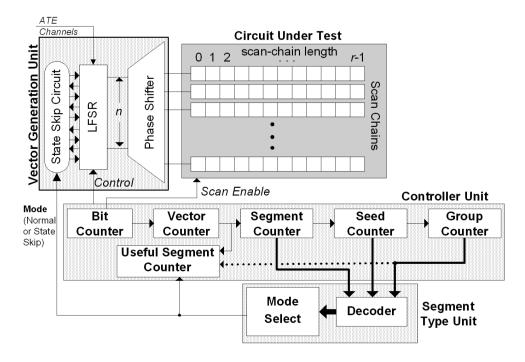

|          |      | 3.4.1 Decompression Architecture                              | 57 |

|          |      | 3.4.2 Experimental Results                                    | 58 |

|          |      | 3.4.3 Limitations                                             | 61 |

|          | 3.5  | Variable-State-Skip LFSRs                                     | 62 |

|          |      | 3.5.1 VSS_LFSRs Scheme                                        | 63 |

|          |      | 3.5.2 Decompression Architecture                              | 63 |

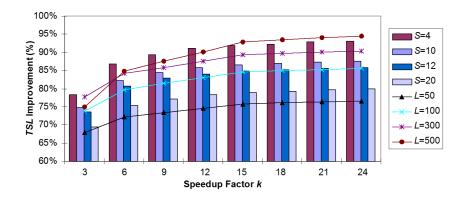

|          |      | 3.5.3 Experimental Results of VSS_LFSRs                       | 65 |

|          | 3.6  | Comparisons                                                   | 68 |

|          | 3.7  | Conclusions                                                   | 71 |

| 4        | Self | -Freeze Linear Decompressors for Low Power Testing            | 72 |

|          | 4.1  | Overview                                                      | 72 |

|          | 4.2  | Background                                                    | 73 |

|          | 4.3  | Power Aware Encoding                                          | 75 |

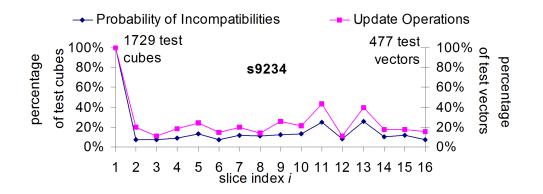

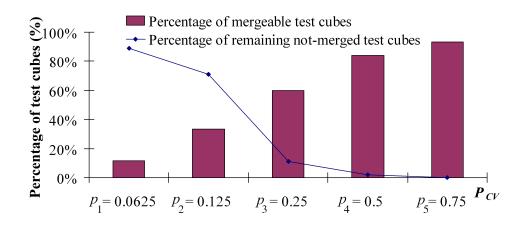

|          |      | 4.3.1 Test Data Analysis                                      |    |

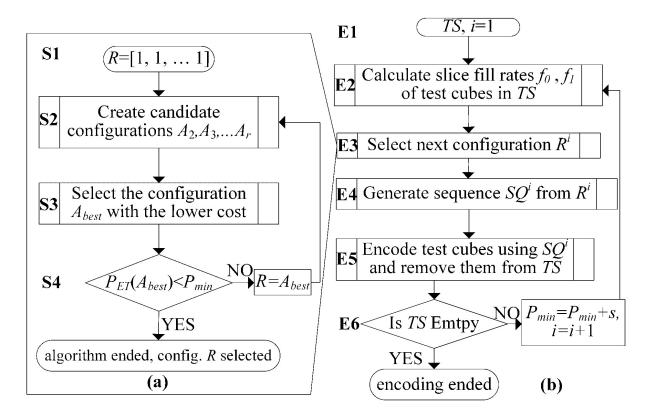

|          |      | 4.3.2 Encoding Algorithm                                      | 79 |

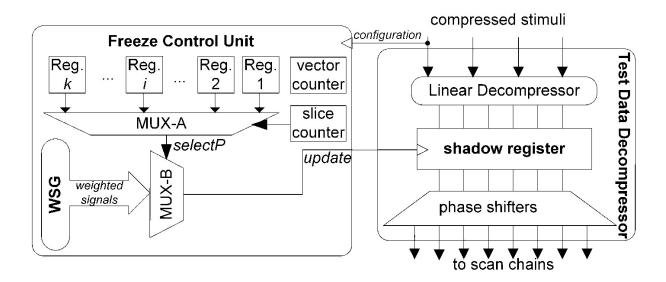

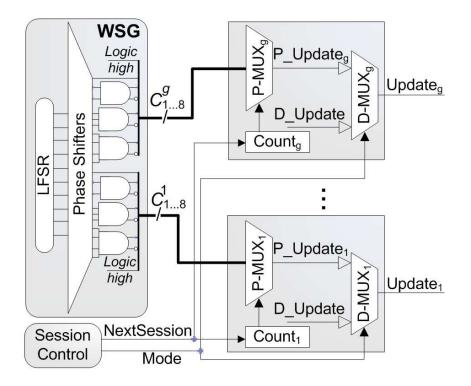

|          | 4.4  | Architecture                                                  | 80 |

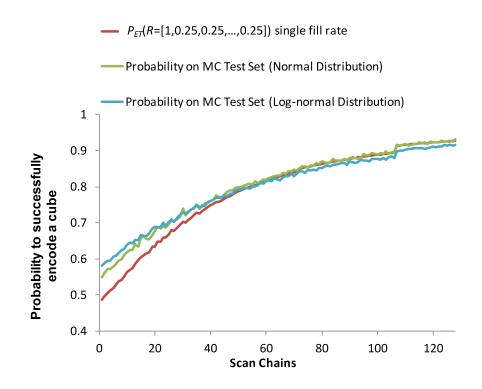

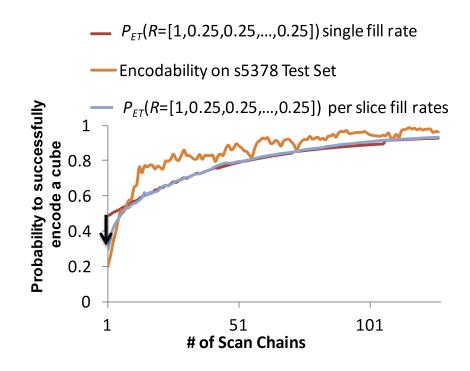

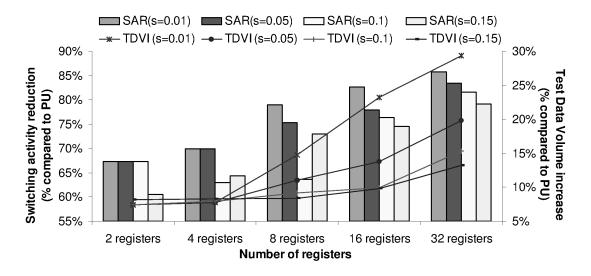

|          | 4.5  | Experiments                                                   | 82 |

|          | 4.6  | Conclusions                                                   | 85 |

| <b>5</b> | Def  | ect Aware X-Filling for Low-Power Testing                     | 86 |

|          | 5.1  | Overview                                                      | 86 |

|          | 5.2  | Modified Fill Adjacent - the new X-Filling Method             | 87 |

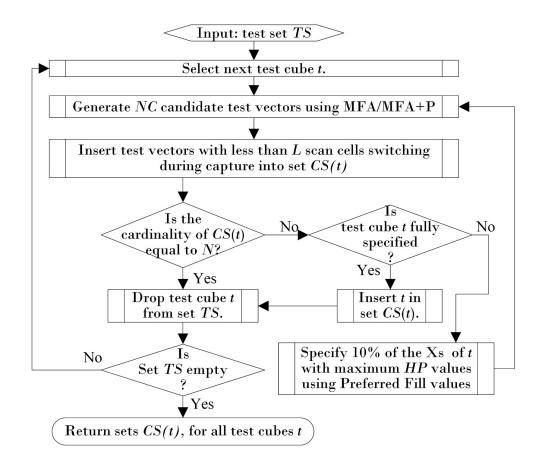

|          |      | 5.2.1 Generation of Power Efficient Candidate Test Vectors    | 87 |

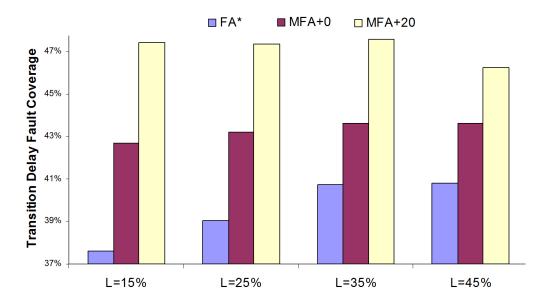

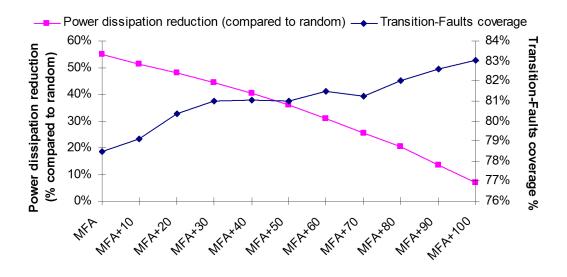

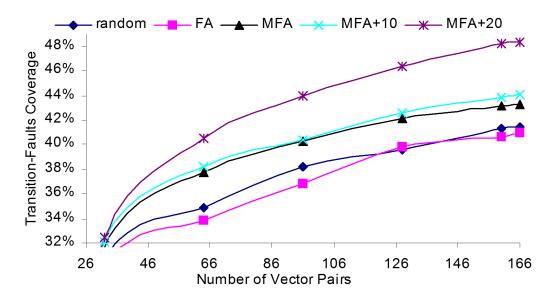

|          |      | 5.2.2 Evaluation and Selection of Test Vectors                | 90 |

|          | 5.3  | Experiments                                                   | 92 |

|          | 5.4  | Conclusions                                                   | 97 |

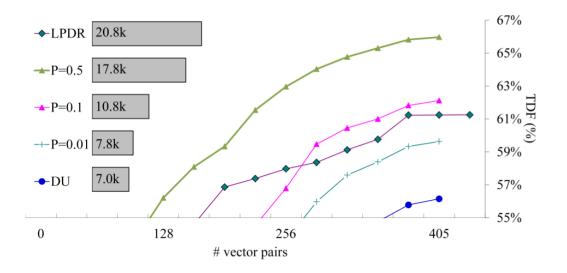

| 6        | LFS  | SR Reseeding Techniques for High-Quality Testing              | 98 |

| 5        | 6.1  | Overview                                                      | 98 |

|          | 6.2  | Motivation                                                    | 99 |

|          |      |                                                               |    |

|   | 6.3 | A Dev  | riation-based Metric for Time-related Defects         | . 102 |

|---|-----|--------|-------------------------------------------------------|-------|

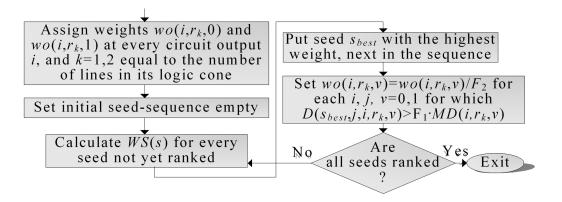

|   | 6.4 | Gener  | ation of Defect-Aware Seeds                           | . 104 |

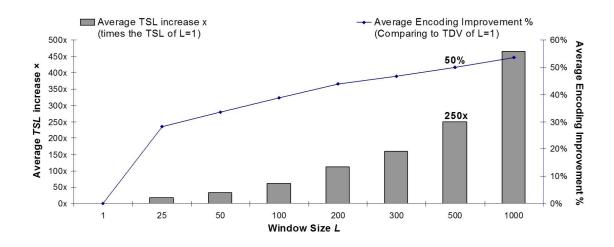

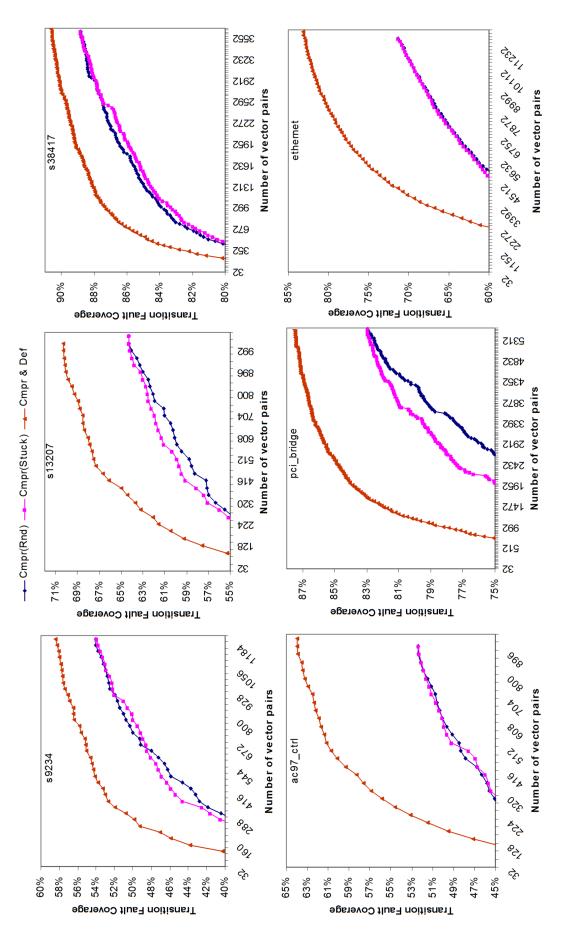

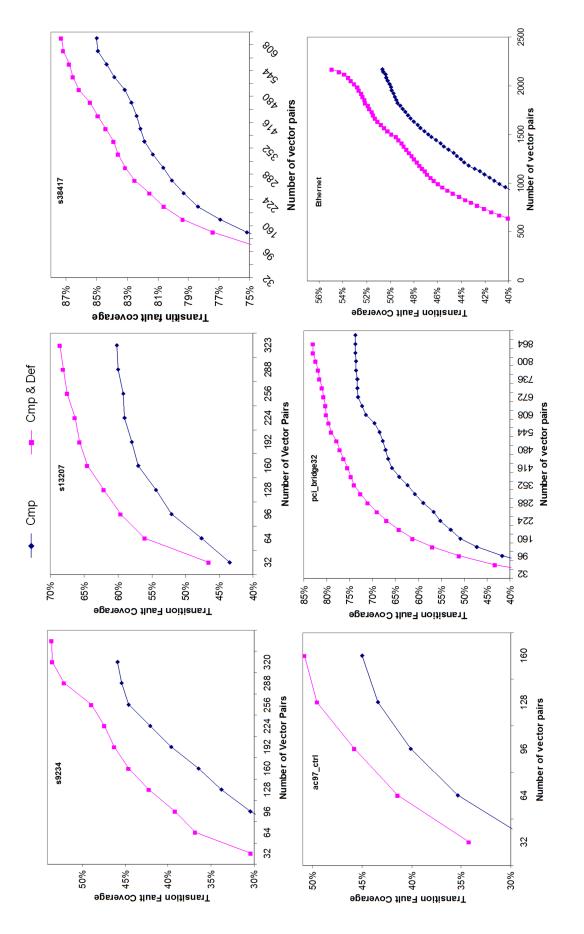

|   |     | 6.4.1  | Window-Based Reseeding                                | . 104 |

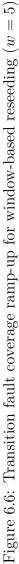

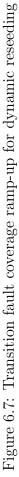

|   |     | 6.4.2  | Classical Static LFSR Reseeding and Dynamic Reseeding | . 108 |

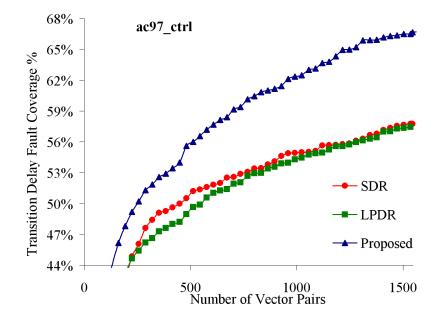

|   | 6.5 | Fault  | simulation Results                                    | . 111 |

|   | 6.6 | Conclu | usions                                                | . 117 |

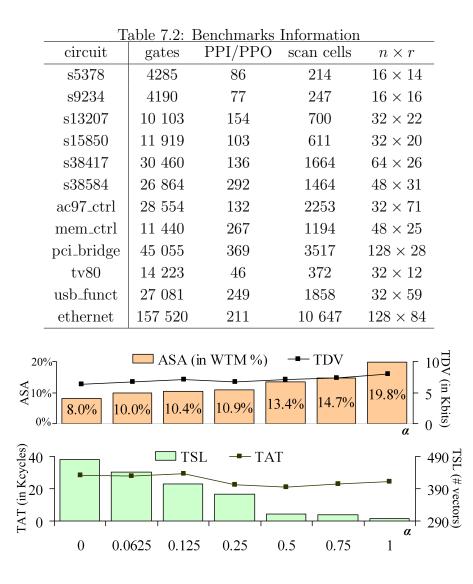

| 7 | Low | -Powe  | er and High-Quality Test Data Compression             | 120   |

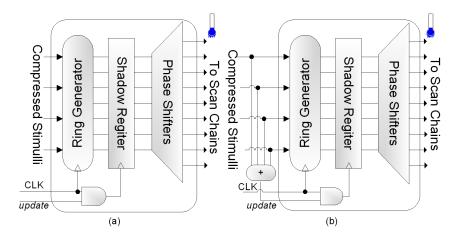

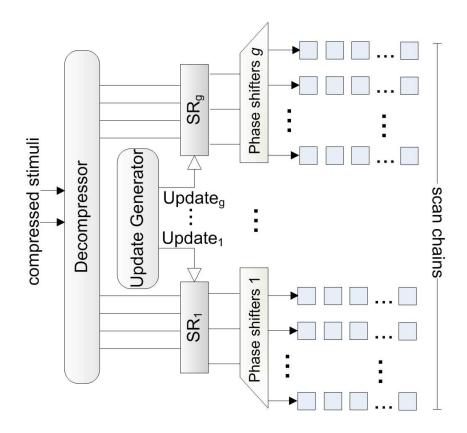

|   | 7.1 | Linear | -based Decompressor                                   | . 120 |

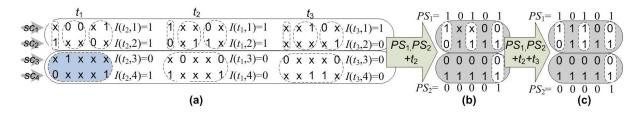

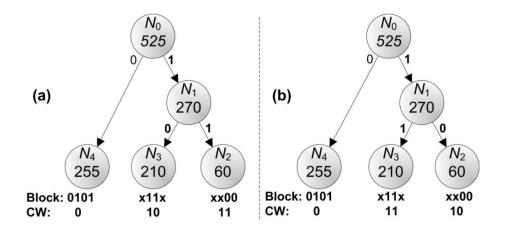

|   |     | 7.1.1  | Motivational Example                                  | . 121 |

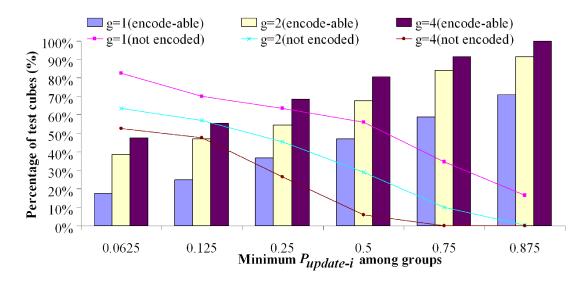

|   |     | 7.1.2  | Proposed Method                                       | . 123 |

|   |     | 7.1.3  | Experimental Results                                  | . 130 |

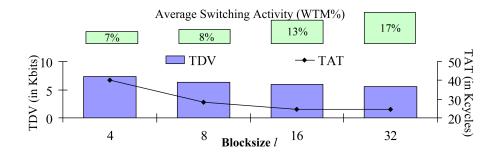

|   | 7.2 | Code-  | based Decompressor                                    | . 135 |

|   |     | 7.2.1  | Motivation                                            | . 136 |

|   |     | 7.2.2  | Basic Idea                                            | . 137 |

|   |     | 7.2.3  | Encoding Method                                       | . 139 |

|   |     | 7.2.4  | Unmodeled Defect Coverage Improvement                 | . 146 |

|   |     | 7.2.5  | Decompression Architecture                            | . 147 |

|   |     | 7.2.6  | Experimental Results                                  | . 152 |

|   | 7.3 | Conclu | usions                                                | . 160 |

| 8 | Con | clusio | ns                                                    | 161   |

# LIST OF FIGURES

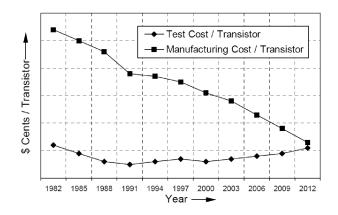

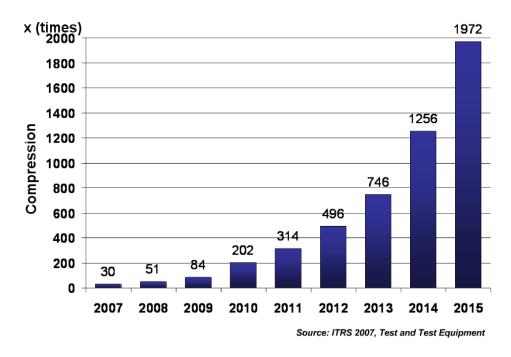

| 1.1                                                                                                                                           | ITRS'07 test cost predictions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 2                                                              |

|-----------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|

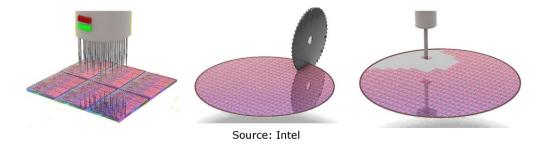

| 1.2                                                                                                                                           | Silicon to ingot and then sliced to create wafers.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 2                                                              |

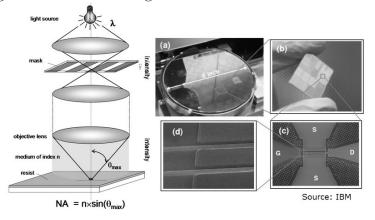

| 1.3                                                                                                                                           | Dies printed on wafer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 2                                                              |

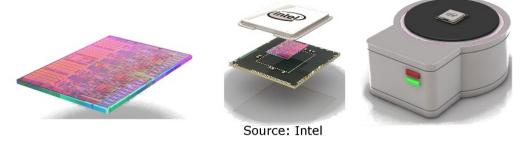

| 1.4                                                                                                                                           | Packaging                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 3                                                              |

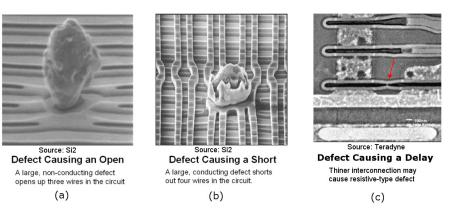

| 1.5                                                                                                                                           | Silicon defects                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 3                                                              |

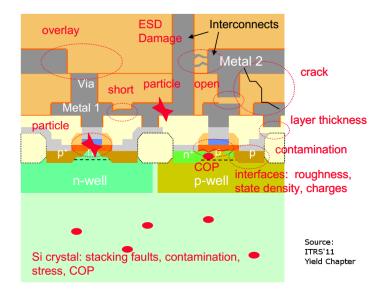

| 1.6                                                                                                                                           | Possible causes of failures                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 4                                                              |

| 1.7                                                                                                                                           | Structural testing, wafer slicing and faulty die disard                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 5                                                              |

| 1.8                                                                                                                                           | KGD packaging and functional testing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 5                                                              |

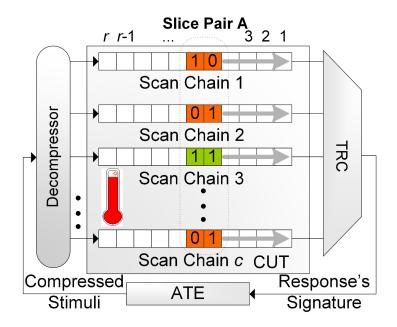

| 1.9                                                                                                                                           | Basic Testing Approach.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 6                                                              |

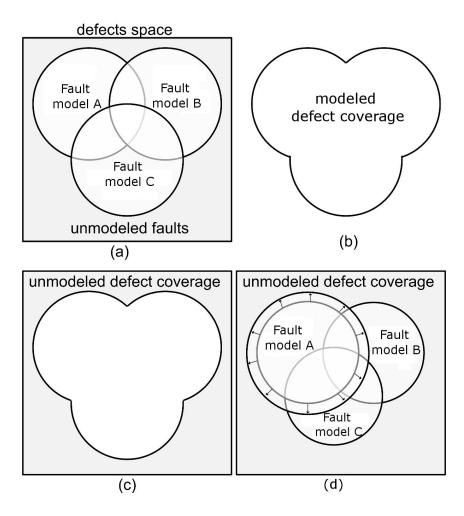

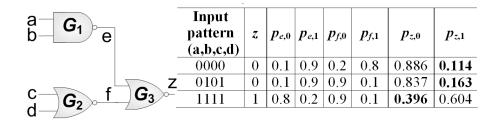

| 1.10                                                                                                                                          | Unmodeled defect coverage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 8                                                              |

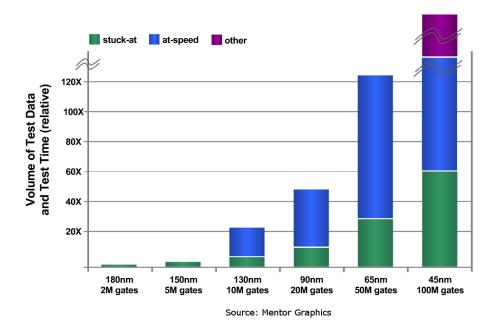

| 1.11                                                                                                                                          | Explosion of test data volume                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 9                                                              |

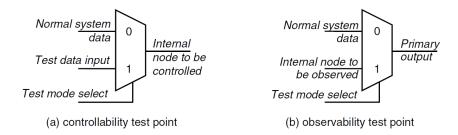

| 1.12                                                                                                                                          | DFT test point                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 11                                                             |

| 1.13                                                                                                                                          | Adding test points at a sequential circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 11                                                             |

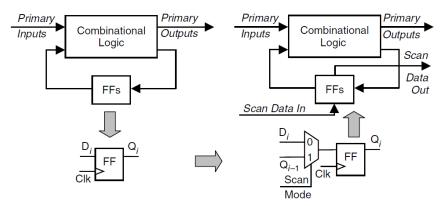

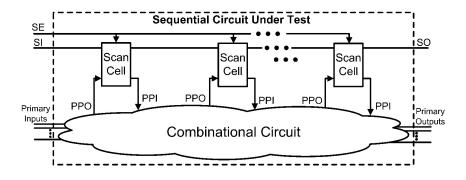

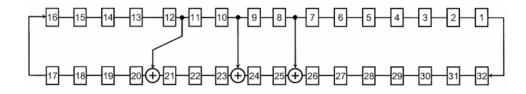

| 1.14                                                                                                                                          | A typical scan design                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 12                                                             |

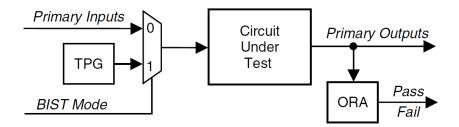

| 1.15                                                                                                                                          | BIST scheme.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 13                                                             |

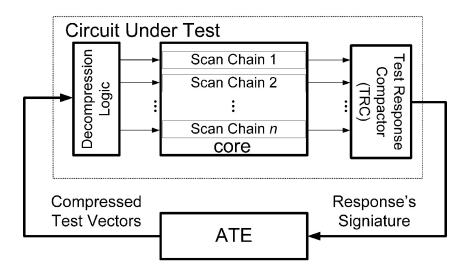

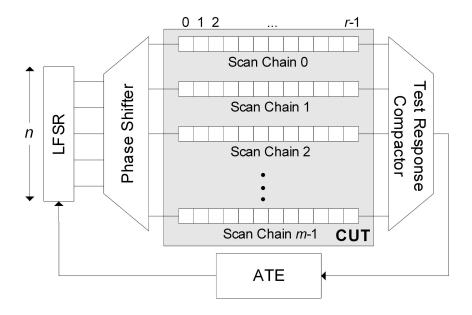

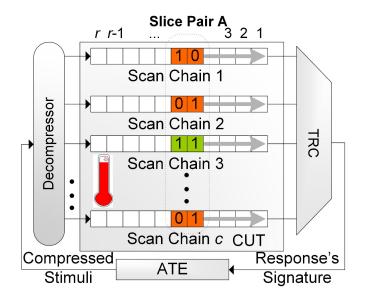

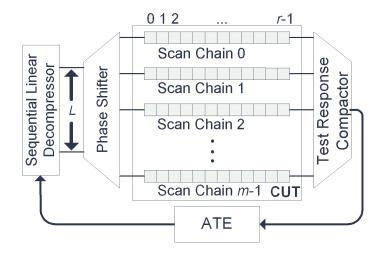

| 1.16                                                                                                                                          | Test Resource Partitioning Architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 14                                                             |

|                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                |

| 1.17                                                                                                                                          | ITRS'07 compression prediction requirements                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 15                                                             |

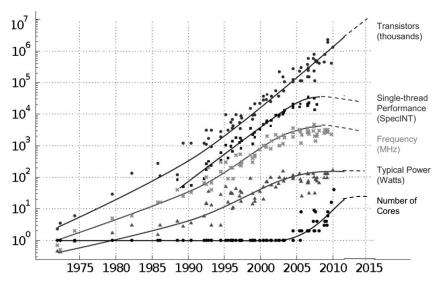

|                                                                                                                                               | Moore's Law in Respect to Transistors Number, Single Thread Perfor-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 15                                                             |

|                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 15<br>16                                                       |

|                                                                                                                                               | Moore's Law in Respect to Transistors Number, Single Thread Perfor-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                |

| 1.18                                                                                                                                          | Moore's Law in Respect to Transistors Number, Single Thread Performance, Frequency, Power and Number of Cores                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 16                                                             |

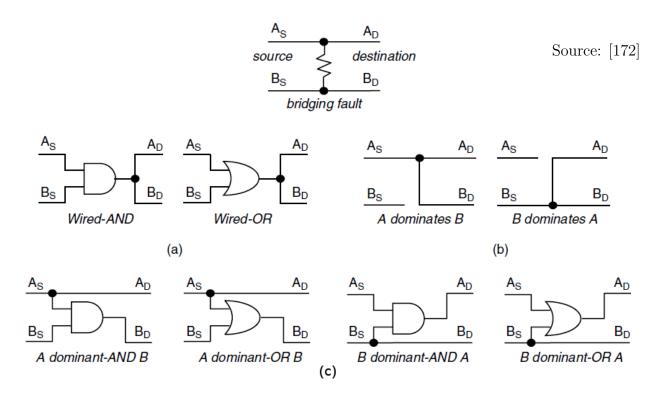

| 1.18<br>2.1                                                                                                                                   | Moore's Law in Respect to Transistors Number, Single Thread Performance, Frequency, Power and Number of CoresSingle Thread Performance, Single Thread Performance, Frequency, Power and Number of CoresBridging fault modelsSingle Thread Performance, Single Thread Perfo | 16<br>22                                                       |

| <ol> <li>1.18</li> <li>2.1</li> <li>2.2</li> </ol>                                                                                            | Moore's Law in Respect to Transistors Number, Single Thread Perfor-<br>mance, Frequency, Power and Number of Cores                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 16<br>22<br>27                                                 |

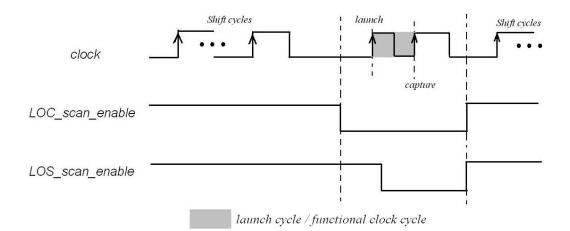

| <ol> <li>1.18</li> <li>2.1</li> <li>2.2</li> <li>2.3</li> </ol>                                                                               | Moore's Law in Respect to Transistors Number, Single Thread Performance, Frequency, Power and Number of CoresSingle Thread Performance, Frequency, Power and Number of CoresBridging fault modelsSubscriptionLOC and LOS operation for delay testingSubscriptionOutput deviations exampleSubscription                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 16<br>22<br>27<br>30                                           |

| <ol> <li>1.18</li> <li>2.1</li> <li>2.2</li> <li>2.3</li> <li>2.4</li> </ol>                                                                  | Moore's Law in Respect to Transistors Number, Single Thread Performance, Frequency, Power and Number of CoresSingle Thread Performance, Frequency, Power and Number of CoresBridging fault modelsSubstrateLOC and LOS operation for delay testingSubstrateOutput deviations exampleSubstrateClassical LFSR-based decompression architectureSubstrate                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 16<br>22<br>27<br>30<br>33                                     |

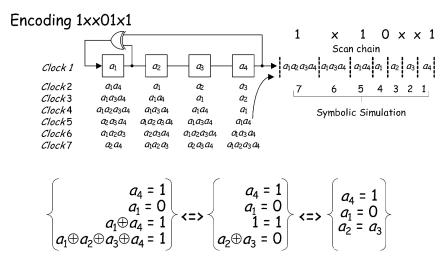

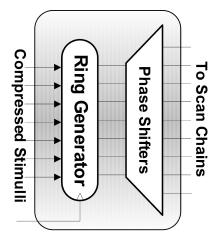

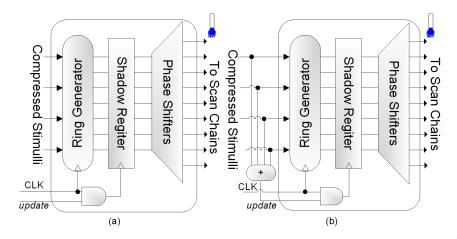

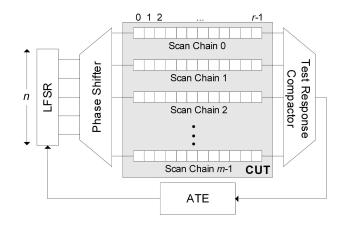

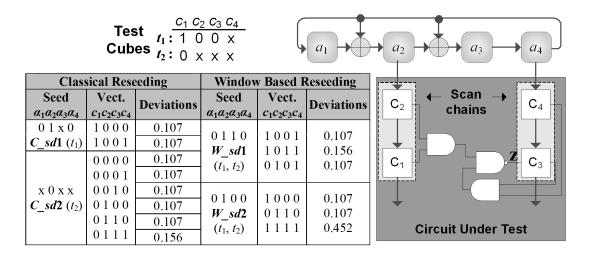

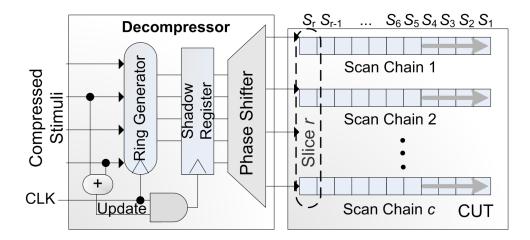

| <ol> <li>1.18</li> <li>2.1</li> <li>2.2</li> <li>2.3</li> <li>2.4</li> <li>2.5</li> </ol>                                                     | Moore's Law in Respect to Transistors Number, Single Thread Performance, Frequency, Power and Number of CoresSingle Thread Performance, Frequency, Power and Number of CoresBridging fault modelsSubscriptionLOC and LOS operation for delay testingSubscriptionOutput deviations exampleSubscriptionClassical LFSR-based decompression architectureSubscriptionClassical LFSR reseeding exampleSubscription                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 16<br>22<br>27<br>30<br>33<br>34                               |

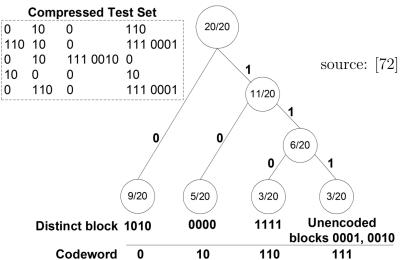

| <ol> <li>1.18</li> <li>2.1</li> <li>2.2</li> <li>2.3</li> <li>2.4</li> <li>2.5</li> <li>2.6</li> </ol>                                        | Moore's Law in Respect to Transistors Number, Single Thread Perfor-<br>mance, Frequency, Power and Number of Cores                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 16<br>22<br>27<br>30<br>33<br>34<br>35                         |

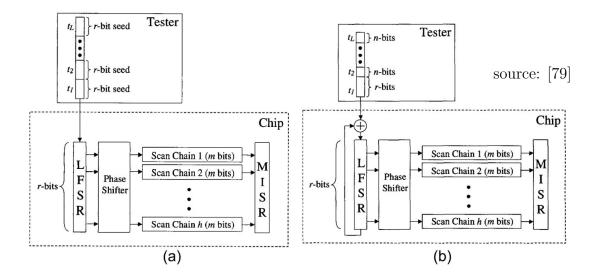

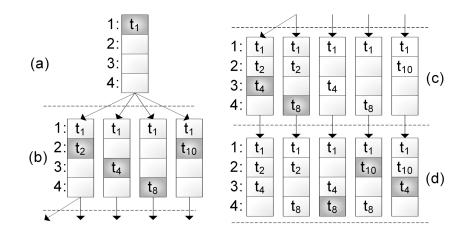

| <ol> <li>1.18</li> <li>2.1</li> <li>2.2</li> <li>2.3</li> <li>2.4</li> <li>2.5</li> <li>2.6</li> <li>2.7</li> </ol>                           | Moore's Law in Respect to Transistors Number, Single Thread Performance, Frequency, Power and Number of CoresSingle Thread Performance, Frequency, Power and Number of CoresBridging fault modelsSubstrateLOC and LOS operation for delay testingSubstrateOutput deviations exampleSubstrateClassical LFSR-based decompression architectureSubstrateClassical LFSR reseeding exampleSubstrate(a) Static reseeding versus (b) dynamic reseedingSubstrate                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 16<br>22<br>27<br>30<br>33<br>34<br>35<br>36                   |