## Αποτελεσματικές Τεχνικές Συγχρονισμού για Συστήματα Διαμοιραζόμενης Μνήμης

#### Η ΔΙΔΑΚΤΟΡΙΚΗ ΔΙΑΤΡΙΒΗ

υποβάλλεται στην ορισθείσα από την Γενική Συνέλευση Ειδικής Σύνθεσης του Τμήματος Πληροφορικής Εξεταστική Επιτροπή

από τον

Νιχόλαο Καλλιμάνη

ως μέρος των Υποχρεώσεων για τη λήψη του

ΔΙΔΑΚΤΟΡΙΚΟΥ ΔΙΠΛΩΜΑΤΟΣ ΣΤΗΝ ΠΛΗΡΟΦΟΡΙΚΗ

Πανεπιστήμιο Ιωαννίνων Μάιος 2013

#### Τριμελής Συμβουλευτική Επιτροπή (αλφαβητικά)

- Βασίλειος Δημακόπουλος, Αναπληρωτής Καθηγητής του Τμήματος Πληροφορικής του Πανεπιστημίου Ιωαννίνων

- Λεωνίδας Παληός, Αναπληρωτής Καθηγητής του Τμήματος Πληροφορικής του Πανεπιστημίου Ιωαννίνων

- Παναγιώτα Φατούρου, Επίκουρη Καθηγήτρια του Τμήματος Επιστήμης Υπολογιστών του Πανεπιστημίου Κρήτης

#### Επταμελής Εξεταστική Επιτροπή (αλφαβητικά)

- Βασίλειος Δημακόπουλος, Αναπληρωτής Καθηγητής του Τμήματος Πληροφορικής του Πανεπιστημίου Ιωαννίνων

- Απόστολος Ζάρρας, Επίκουρος Καθηγητής του Τμήματος Πληροφορικής του Πανεπιστημίου Ιωαννίνων

- **Κωνσταντίνος Μαγκούτης**, Ερευνητής Γ΄ του Ινστιτούτου Πληροφορικής, Τουμα Τεχνολογίας και Έρευνας

- Δημήτριος Νικολόπουλος, Καθηγητής της Σχολής Electronics Engineering and Computer Science του Πανεπιστημίου Queens University of Belfast

- Λεωνίδας Παληός, Αναπληρωτής Καθηγητής του Τμήματος Πληροφορικής του Πανεπιστημίου Ιωαννίνων

- Ευαγγελία Πιτουρά, Καθηγήτρια του Τμήματος Πληροφορικής του Πανεπιστημίου Ιωαννίνων

- Παναγιώτα Φατούρου, Επίκουρη Καθηγήτρια του Τμήματος Επιστήμης Υπολογιστών του Πανεπιστημίου Κρήτης

## DEDICATION

This dissertation is dedicated to my family.

### ACKNOWLEDGMENTS

First, I would like to sincerely thank my supervisor Panagiota Fatourou for motivating and encouraging me during the entire period that I was conducting my PhD. I would also like to thank the members of my advisory committee, Vassilios Dimakopoulos and Leonidas Palios for their support. Many thanks to Dimitris Nikolopoulos for arranging the provision of access to some of the multi-core machines of the Department of Computer Science at Virginia Tech where I ran some of the experiments of this dissertation, and to Michael Scott for providing me access to the Rochester's Niagara 2 machine. I would also like to thank the rest of the members of my examination committee, Kostas Magoutis, Evaggelia Pitoura, and Apostolos Zarras.

Special thanks go to my friends Spiros Agathos, Eytychia Datsika, Vasilis Kagias, Kostas Lillis, Thanos Mpiliris, Odysseas Petrocheilos, and Kostas Ramantas for supporting and encouraging me.

Finally, I would like to thank Empirikion Foundation for the moral and financial support.

# Contents

| 1 | Intr | oducti   | on                                                    | 2  |

|---|------|----------|-------------------------------------------------------|----|

| 2 | Rela | ated W   | Vork                                                  | 14 |

| 3 | Mo   | del      |                                                       | 22 |

|   | 3.1  | Genera   | al                                                    | 22 |

|   | 3.2  | Pseude   | ocode conventions                                     | 26 |

| 4 | Ada  | aptive   | Wait-Free Synchronization Algorithms                  | 28 |

|   | 4.1  | The F    | -RedBlue algorithm                                    | 28 |

|   |      | 4.1.1    | Algorithm description                                 | 29 |

|   |      | 4.1.2    | Correctness proof                                     | 34 |

|   | 4.2  | Modifi   | ied version of F-RedBlue that uses small base objects | 51 |

|   | 4.3  | Adapt    | ive synchronization algorithms for large objects      | 54 |

| 5 | Pra  | ctical ' | Wait-Free Synchronization Algorithms                  | 60 |

|   | 5.1  | The Si   | im algorithm                                          | 61 |

|   |      | 5.1.1    | Algorithm description                                 | 61 |

|   |      | 5.1.2    | Correctness proof                                     | 63 |

|   |      | 5.1.3    | An efficient implementation of COLLECT                | 69 |

|   |      | 5.1.4    | Space and step complexity                             | 70 |

|   |      | 5.1.5    | Derived lower bounds                                  | 70 |

|   | 5.2  | P-Sim:   | A practical version of Sim                            | 71 |

|   |      | 5.2.1    | Algorithm description                                 | 71 |

|   |      | 5.2.2    | Correctness proof                                     | 74 |

|   |      | 5.2.3    | Space and step complexity                             | 78 |

|                                                                                                                                                                              |     | 5.2.4                                                              | ${\rm Making}\ {\sf P\text{-}Sim}\ {\rm adaptive}\ \dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots$ | 78  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|--------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|                                                                                                                                                                              | 5.3 |                                                                    |                                                                                                                                                                                                                                          |     |

|                                                                                                                                                                              | 5.4 | L-Sim:                                                             | A synchronization algorithm for large objects                                                                                                                                                                                            | 89  |

|                                                                                                                                                                              |     | 5.4.1                                                              | Algorithm description                                                                                                                                                                                                                    | 89  |

|                                                                                                                                                                              |     | 5.4.2                                                              | Correctness proof                                                                                                                                                                                                                        | 93  |

|                                                                                                                                                                              | 5.5 | SimSta                                                             | ack: A wait-free implementation of a shared stack                                                                                                                                                                                        | 104 |

|                                                                                                                                                                              |     | 5.5.1                                                              | Algorithm description                                                                                                                                                                                                                    | 104 |

|                                                                                                                                                                              |     | 5.5.2                                                              | Performance Evaluation                                                                                                                                                                                                                   | 105 |

|                                                                                                                                                                              | 5.6 | SimQu                                                              | eue: A wait-free implementation of a shared queue                                                                                                                                                                                        | 107 |

|                                                                                                                                                                              |     | 5.6.1                                                              | Algorithm description                                                                                                                                                                                                                    | 107 |

|                                                                                                                                                                              |     | 5.6.2                                                              | Correctness proof                                                                                                                                                                                                                        | 110 |

|                                                                                                                                                                              |     | 5.6.3                                                              | Performance evaluation                                                                                                                                                                                                                   | 119 |

| 6                                                                                                                                                                            | Hig | hly-Eff                                                            | icient Blocking Synchronization Algorithms                                                                                                                                                                                               | 121 |

|                                                                                                                                                                              | 6.1 | CC-Syr                                                             | nch: An efficient synchronization algorithm for the CC model                                                                                                                                                                             | 121 |

|                                                                                                                                                                              |     | 6.1.1                                                              | Algorithm description                                                                                                                                                                                                                    | 122 |

|                                                                                                                                                                              |     | 6.1.2                                                              | Time and space complexity                                                                                                                                                                                                                | 124 |

|                                                                                                                                                                              |     | 6.1.3                                                              | Required memory barriers                                                                                                                                                                                                                 | 124 |

|                                                                                                                                                                              |     | 6.1.4                                                              | Correctness proof                                                                                                                                                                                                                        | 125 |

| <ul> <li>6.2 H-Synch: A hierarchical synchronization algorithm based on CC-Synch</li> <li>6.3 DSM-Synch: An efficient synchronization algorithm for the DSM model</li> </ul> |     | ch: A hierarchical synchronization algorithm based on CC-Synch     | 140                                                                                                                                                                                                                                      |     |

|                                                                                                                                                                              |     | Synch: An efficient synchronization algorithm for the DSM model $$ | 142                                                                                                                                                                                                                                      |     |

|                                                                                                                                                                              |     | 6.3.1                                                              | Algorithm description                                                                                                                                                                                                                    | 142 |

|                                                                                                                                                                              |     | 6.3.2                                                              | Time and Space complexity                                                                                                                                                                                                                | 143 |

|                                                                                                                                                                              |     | 6.3.3                                                              | Required memory barriers                                                                                                                                                                                                                 | 143 |

|                                                                                                                                                                              |     | 6.3.4                                                              | Correctness proof                                                                                                                                                                                                                        | 145 |

|                                                                                                                                                                              | 6.4 | Perform                                                            | mance evaluation of CC-Synch, DSM-Synch and H-Synch                                                                                                                                                                                      | 156 |

|                                                                                                                                                                              | 6.5 | Highly                                                             | -efficient blocking data structures                                                                                                                                                                                                      | 163 |

| 7                                                                                                                                                                            | Con | nclusion                                                           | as and Future Work                                                                                                                                                                                                                       | 167 |

# List of Figures

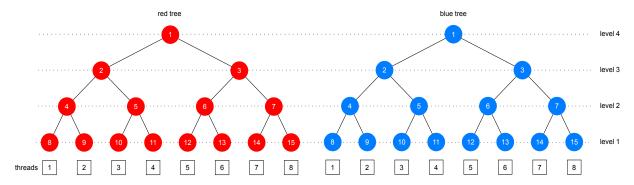

| 4.1  | The red and the blue tree of F-RedBlue for $n=8$                                | 30  |

|------|---------------------------------------------------------------------------------|-----|

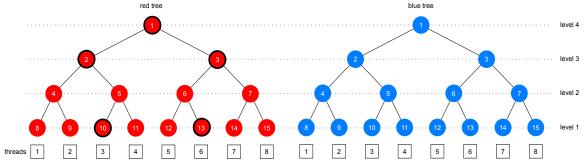

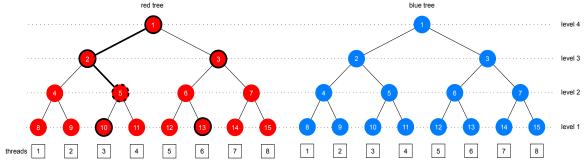

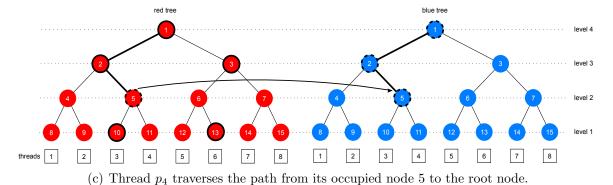

| 4.2  | An example of an execution of F-RedBlue, where thread $p_4$ applies an op-      |     |

|      | eration to the simulated object                                                 | 33  |

| 4.3  | An example of an execution of F-RedBlue                                         | 40  |

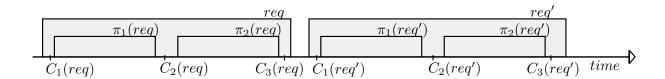

| 5.1  | An example execution of the Sim algorithm                                       | 65  |

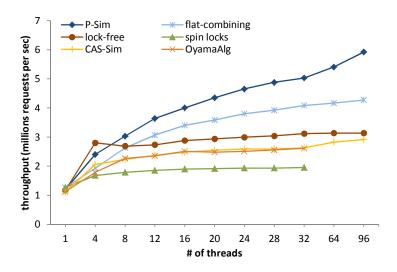

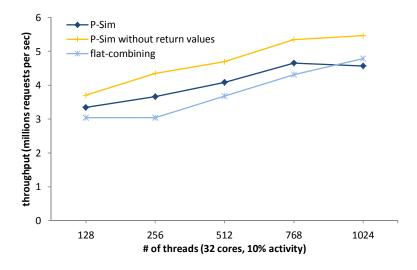

| 5.2  | Performance of P-Sim                                                            | 81  |

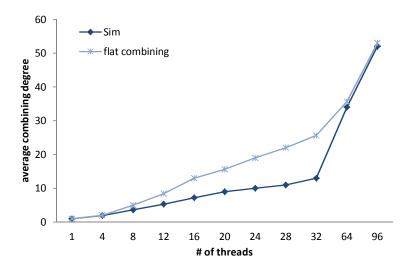

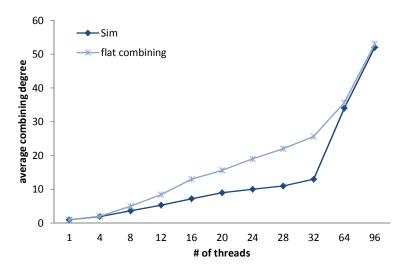

| 5.3  | Average combining degree of P-Sim and flat-combining for different num-         |     |

|      | bers of threads                                                                 | 82  |

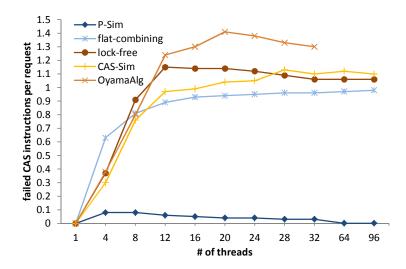

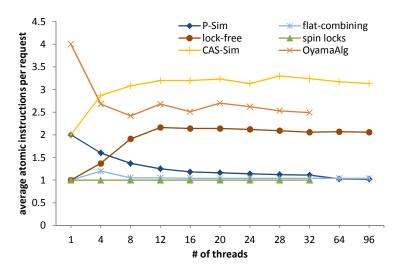

| 5.4  | Average number of failed CAS instructions per request for different numbers     |     |

|      | of threads                                                                      | 83  |

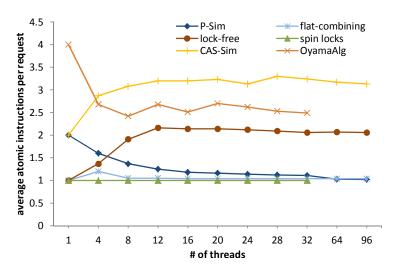

| 5.5  | Average number of atomic instructions (excluding Read and Write opera-          |     |

|      | tions) per request performed by $P\text{-}Sim$ for different numbers of threads | 83  |

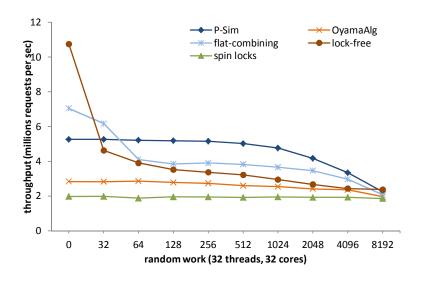

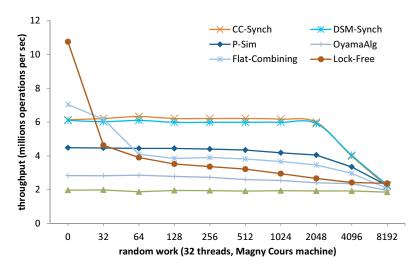

| 5.6  | Performance of P-Sim for different values of random work                        | 86  |

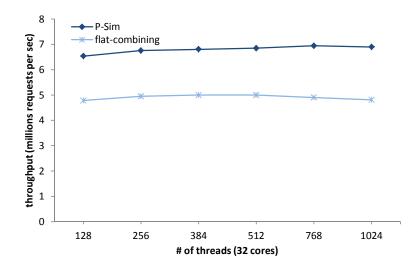

| 5.7  | Performance of P-Sim for large numbers of threads                               | 87  |

| 5.8  | Performance of P-Sim when a large number of threads are initiated but           |     |

|      | only 10% are active                                                             | 87  |

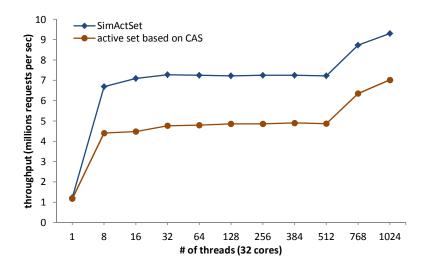

| 5.9  | Performance of SimActSet                                                        | 88  |

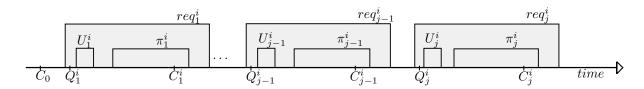

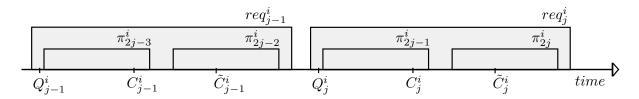

| 5.10 | An example of an execution of L-Sim                                             | 96  |

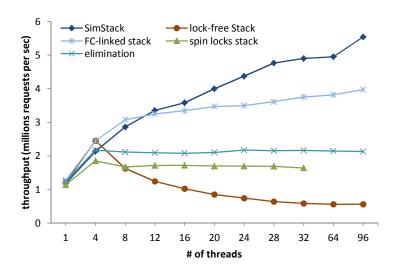

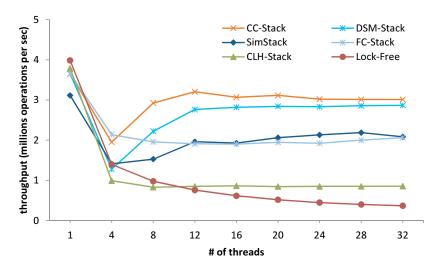

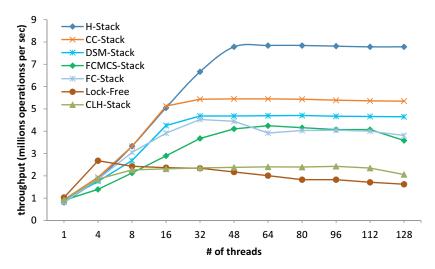

| 5.11 | Performance of SimStack                                                         | 106 |

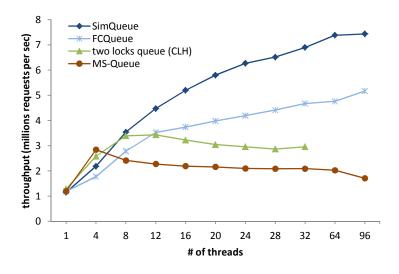

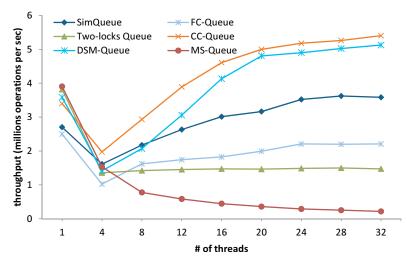

| 5.12 | Performance of SimQueue                                                         | 119 |

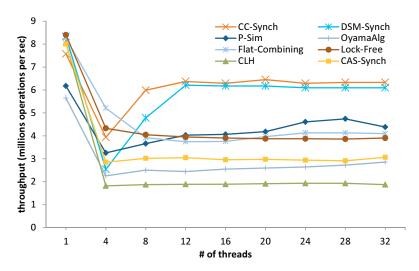

| 6.1  | Average throughput of CC-Synch and DSM-Synch on the Magny Cours                 |     |

|      | machine while simulating a Fetch&Multiply object                                | 157 |

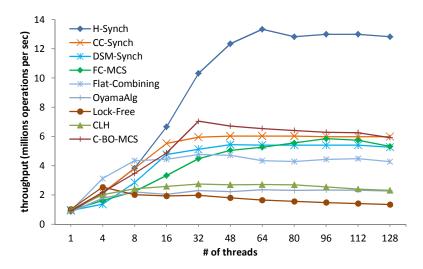

| 6.2  | Average throughput of CC-Synch, DSM-Synch and H-Synch on the Niagara            |     |

|      | 2 machine while simulating a Fetch&Multiply object                              | 159 |

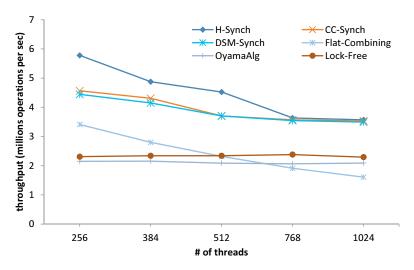

| 6.3  | Average throughput of CC-Synch, DSM-Synch and H-Synch on the Niagara 2                     |     |

|------|--------------------------------------------------------------------------------------------|-----|

|      | machine for $n>128$ (over-subscribing) while simulating a Fetch&Multiply                   |     |

|      | object                                                                                     | 160 |

| 6.4  | Average degree of combining of CC-Synch, DSM-Synch and H-Synch while                       |     |

|      | simulating a Fetch&Multiply object                                                         | 161 |

| 6.5  | Average number of atomic instructions (CAS, Swap and Add) that CC-Synch,                   |     |

|      | DSM-Synch and H-Synch execute on the Niagara 2 machine while simulating                    |     |

|      | a Fetch&Multiply object                                                                    | 162 |

| 6.6  | Average throughput of CC-Synch, DSM-Synch and H-Synch for different                        |     |

|      | values of random work                                                                      | 163 |

| 6.7  | Average throughput of CC-Stack and DSM-Stack on the Magny Cours ma-                        |     |

|      | chine                                                                                      | 164 |

| 6.8  | Average throughput of $CC	ext{-}Stack,\ DSM	ext{-}Stack$ and $H	ext{-}Stack$ the Niagara 2 |     |

|      | machine                                                                                    | 165 |

| 6.9  | Average throughput of CC-Queue and DSM-Queue on the Magny Cours                            |     |

|      | machine                                                                                    | 165 |

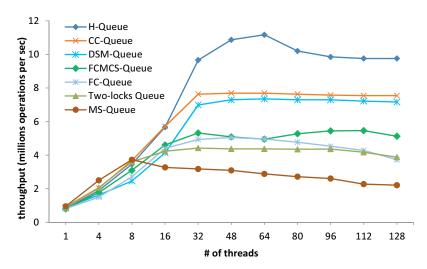

| 6.10 | Average throughput of CC-Queue, DSM-Queue and H-Queue on the Niagara                       |     |

|      | 2 machine                                                                                  | 166 |

# LIST OF TABLES

| 1.1 | Algorithms and their properties proposed in this dissertation          |

|-----|------------------------------------------------------------------------|

| 2.1 | Wait-free universal algorithms and their complexities                  |

| 5.1 | Notation used in the proof of Sim                                      |

| 5.2 | Notation used in the proof of P-Sim                                    |

| 5.3 | Average cpu cycles spent in cpu stalls per request for P-Sim and flat- |

|     | combining for $n = 16$                                                 |

| 5.4 | Sensitivity of P-Sim to the backoff upper bound parameter              |

| 5.5 | Notation used in the proof of L-Sim                                    |

| 6.1 | Notation used in the proof of CC-Synch                                 |

| 6.2 | Notation used in the proof of DSM-Synch                                |

| 6.3 | Cache misses and memory stalls per operation for $n=16$ of CC-Synch,   |

|     | P-Sim and flat-combining                                               |

# List of Algorithms

| 1  | Pseudocode for F-RedBlue                                            |

|----|---------------------------------------------------------------------|

| 2  | Pseudocode for Calculate and Propagate of F-RedBlue                 |

| 3  | Pseudocode for S-RedBlue                                            |

| 4  | Pseudocode for Propagate and Calculate of S-RedBlue                 |

| 5  | Pseudocode for LS-RedBlue                                           |

| 6  | Pseudocode for BLS-RedBlue                                          |

| 7  | Pseudocode for Calculate of BLS-RedBlue 58                          |

| 8  | Pseudocode for Sim                                                  |

| 9  | Data structures used in P-Sim                                       |

| 10 | Pseudocode of P-Sim                                                 |

| 11 | Data structures used in L-Sim and pseudocode for LSIMAPPLYOP 91     |

| 12 | Pseudocode for L-Sim                                                |

| 13 | Implementation of Pop and Push for SimStack                         |

| 14 | Data structures for SimQueue, the implementation of ENQUEUE and DE- |

|    | QUEUE in SimQueue, and the implementations (enqueue and dequeue) of |

|    | the sequential versions of enqueue and dequeue                      |

| 15 | Pseudocode for the Attempt in SimQueue                              |

| 16 | Pseudocode for EnqLinkQueue and DeqLinkQueue in SimQueue 110        |

| 17 | Pseudocode for CC-Synch                                             |

| 18 | Pseudocode for H-Synch                                              |

| 19 | Pseudocode for DSM-Synch                                            |

### Abstract

Nikolaos D. Kallimanis.

Highly-Efficient Synchronization Techniques in Shared-Memory Distributed Systems.

PhD, Department of Computer Science, University of Ioannina, Greece.

May, 2013.

Thesis Supervisor: Vassilios Dimakopoulos.

Overcoming the difficulty of concurrent programming has never become more urgent due to the proliferation of multicore machines and the imperative necessity of exploiting their computational power. One way to achieve this is by designing efficient concurrent data structures; common structures, like stacks and queues, are the most widely used interthread communication mechanisms. Additionally, synchronization techniques are required to efficiently execute, in a concurrent environment, those parts of modern applications that require significant synchronization. Although the efficient parallelization of these parts is not an easy task, Amdhal's law implies that achieving this is necessary in order to avoid significant reductions in speed-up.

In this dissertation three families of highly efficient synchronization algorithms, called RedBlue, Sim and Synch are presented for executing concurrently blocks of code that have originally been programmed to be executed sequentially in asynchronous shared-memory distributed systems.

We start by presenting the RedBlue family of adaptive synchronization algorithms that use common base objects (LL/SC or CAS and Read-Write) provided by the majority of the real-world machines. The first of these algorithms achieves better time complexity than all previously presented algorithms and it matches a lower bound presented by Jayanti in PODC 1998. This algorithm uses large LL/SC base objects and it comprises the keystone for the design of the other RedBlue algorithms that use smaller base objects. Specifically,

the second algorithm significantly reduces the size of the required base objects. The last two algorithms have been designed for large objects improving previously presented work for large objects.

In the Sim family of synchronization algorithms, we aim at (1) getting better time complexity by using base objects other than LL/SC and read-write (i.e. Swap, Add, etc) and (2) competing in terms of performance with the state-of-the-art synchronization algorithms (i.e. high performance spin-locks, etc), while having the nice theoretical properties that RedBlue algorithms have. Sim algorithms achieve these goals.

Sim is a simple synchronization algorithm with constant step complexity using an Add additional to an LL/SC object. Sim answers the open problem that was mentioned by Jayanti in PODC 1998: "If shared-memory supports all of Read, Write, LL/SC, Swap, CAS, Move, Add, Fetch&Multiply, would the  $\Omega(logn)$  lower bound still hold?". Sim has been implemented for a real shared-memory machine architecture. Its practical version, called P-Sim, outperforms several state-of-the-art lock-based and lock-free synchronization algorithms, while being wait-free, i.e. satisfying a stronger progress condition than all the algorithms that it outperforms.

The Sim and RedBlue families of synchronization algorithms can be considered as efficient wait-free implementations of the combining technique in which, one thread (the combiner) in addition to its own operation, serves the operations of other active threads. The RedBlue synchronization algorithms are adaptive and employ LL/SC (or CAS) and read-write base objects, whereas Sim are much simpler algorithms that are highly-efficient in practice and require Add base objects.

We further study blocking implementations of the combining technique with the goal of discovering where their real performance power resides and whether or how performance is impacted by ensuring some desired properties (e.g. fairness in serving requests). This is accomplished by presenting two new blocking implementations of the combining technique; the first (CC-Synch) is highly-efficient in systems that support coherent caches, whereas the second (DSM-Synch) works better in cache-less NUMA machines. In comparison to previous blocking implementations, the new implementations (1) provide bounds on the number of remote memory references (RMRs) that they perform, (2) support a stronger notion of fairness, and (3) use simpler and fewer base objects. CC-Synch and DSM-Synch achieve better performance than P-Sim as well as any other algorithm pro-

vided in the past. The experimental analysis sheds light to the questions that were aimed to be answered.

Several modern multicore systems organize the cores into clusters and provide fast communication within the same cluster and much slower communication across clusters. A hierarchical version of CC-Synch, called H-Synch, is presented, which exploits the hierarchical communication nature of such systems to achieve better performance. Experiments show that H-Synch significantly outperforms previous state-of-the-art hierarchical approaches.

Based on P-Sim, CC-Synch, DSM-Synch, and H-Synch, we provide very efficient implementations of common shared data structures like stacks and queues. Specifically, the implementations SimStack and SimQueue that are based on P-Sim are wait-free, whereas those based on CC-Synch, DSM-Synch and H-Synch are blocking but achieve better performance than SimStack and SimQueue as well as any other algorithm provided in the past. SimStack and SimQueue are the first stack and queue implementations that satisfy both wait-freedom and high performance.

The results of this dissertation have been published in the following conferences/journals: ACM PPoPP 2012, ACM SPAA 2011, DISC 2009 and Theory of Computing Systems Special Issue on SPAA 2011.

#### ΕΚΤΕΤΑΜΕΝΗ ΠΕΡΙΛΗΨΗ ΣΤΑ ΕΛΛΗΝΙΚΑ

Νικόλαος Καλλιμάνης του Δημητρίου και της Νικολέττας.

PhD, Τμήμα Πληροφορικής, Πανεπιστήμιο Ιωαννίνων.

Μάιος, 2013.

Αποτελεσματικές Τεχνικές Συγχρονισμού για Συστήματα Διαμοιραζόμενης Μνήμης.

Επιβλέπων: Βασίλειος Δημακόπουλος.

Η εξάπλωση των πολυπύρηνων επεξεργαστών τα τελευταία χρόνια έχει καταστήσει εξαιρετικά αναγκαία την εκμετάλλευση της υπολογιστικής ισχύος τους. Ένας τρόπος για την αποδοτική χρήση συστημάτων που βασίζονται σε πολυπύρηνους επεξεργαστές είναι ο σχεδιασμός αποδοτικών διαμοιραζόμενων (παράλληλα προσπελάσιμων από πολλά νήματα) δομών δεδομένων (π.χ. στοιβών και ουρών), οι οποίες χρησιμοποιούνται ως ένας θεμελιώδης μηχανισμός επικοινωνίας και συγχρονισμού μεταξύ των νημάτων του συστήματος. Η αποτελεσματική παράλληλη εκτέλεση πολλών εφαρμογών επιβάλει την ανάπτυξη αποδοτικών αλγορίθμων συγχρονισμού που θα συγχρονίζουν αποτελεσματικά τα τμήματα των εφαρμογών που εκτελούνται σε διαφορετικά επεξεργαστικά στοιχεία. Ο νόμος του Amdhal υποδεικνύει ότι η χρήση αποδοτικών τεχνικών συγχρονισμού είναι απαραίτητη για την επίτευξη της μέγιστης δυνατής ταχύτητας υπολογισμών.

Σε αυτή τη διατριβή παρουσιάζονται τρεις οικογένειες νέων αλγορίθμων συγχρονισμού εξαιρετικά υψηλής απόδοσης, οι οποίες ονομάζονται RedBlue, Sim και Synch. Οι εν λόγω αλγόριθμοι συγχρονισμού χρησιμοποιούνται για την παράλληλη εκτέλεση κώδικα που έχει προγραμματιστεί να εκτελείται σειριακά.

Αρχικά παρουσιάζονται οι προσαρμοστικοί αλγόριθμοι συγχρονισμού RedBlue (οι προσαρμοστικοί αλγόριθμοι έχουν χρονική πολυπλοκότητα ανάλογη του αριθμού των ενεργών νημάτων), οι οποίοι πληρούν την ιδιότητα ελεύθερη-αναμονής (wait-free) και είναι κατάλληλοι

για ασύγχρονα συστήματα διαμοιραζόμενης μνήμης. Ο πρώτος από αυτούς τους αλγορίθμους, ο οποίος ονομάζεται F-RedBlue, επιτυγχάνει την καλύτερη χρονική πολυπλοκότητα από τους αλγορίθμους που είχαν παρουσιαστεί παλιότερα και είναι χρονικά βέλτιστος αφού επιτυγχάνει το κάτω όριο χρονικής πολυπλοκότητας που παρουσιάστηκε από τον Jayanti στο PODC 1998. Ο δεύτερος αλγόριθμος της οικογένειας RedBlue χρησιμοποιεί βασικά αντικείμενα μικρότερου μεγέθους από ότι ο F-RedBlue ενώ οι δύο τελευταίοι αλγόριθμοι της οικογένειας RedBlue βελτιώνουν τεχνικές που είχαν παρουσιαστεί παλιότερα.

Κατά την ανάπτυξη των Sim αλγορίθμων συγχρονισμού, στόχος ήταν (1) η περαιτέρω μείωση της χρονικής πολυπλοκότητας χρησιμοποιώντας βασικά αντικείμενα διαφορετικά των LL/SC και Read-Write (όπως Swap και Add βασικά αντικείμενα) και (2) η βελτίωση της απόδοσής τους, ώστε οι επιδόσεις τους να είναι τέτοιες που να ανταγωνίζονται ή και να ξεπερνούν τις επιδόσεις των γρηγορότερων αλγορίθμων συγχρονισμού (κλειδώματα, κτλ) έχοντας παράλληλα όλα τα καλά θεωρητικά χαρακτηριστικά των RedBlue αλγορίθμων. Η οικογένεια των Sim αλγορίθμων επιτυγγάνει όλους αυτούς τους στόχους.

Ο αλγόριθμος συγχρονισμού Sim χρησιμοποιεί ένα Add και ένα LL/SC βασικό αντικείμενο και επιτυγχάνει O(1) χρονική πολυπλοκότητα. Ο Sim αλγόριθμος απαντά στο ανοιχτό πρόβλημα που τέθηκε από τον Jayanti στο PODC 1998, για το αν το κάτω όριο  $\Omega(log(n))$  ισχύει στην περίπτωση που η διαμοιραζόμενη μνήμη υποστηρίζει όλα τους τύπους βασικών αντικειμένων Read, Write, LL/SC, Swap, CAS, Move, Add και Fetch&Multiply. H χρονική πολυπλοκότητα του Sim είναι σταθερή, και επομένως η απάντηση στο ερώτημα αυτό είναι αρνητική. H πρακτική έκδοση του Sim αλγορίθμου, που ονομάζεται P-Sim, ξεπερνά σε επιδόσεις τους γρηγορότερους αλγορίθμους συγχρονισμού, ενώ ταυτόχρονα πληροί την ισχυρότερη συνθήκη τερματισμού (ελεύθερη αναμονής).

Οι οιχογένειες των RedBlue και Sim αλγορίθμων συγχρονισμού είναι ουσιαστικά αποδοτικές υλοποιήσεις της συνεργατικής τεχνικής (combining technique), στην οποία ένα νήμα είναι δυνατό να εφαρμόζει λειτουργίες και άλλων νημάτων βοηθώντας τα να τελειώσουν την εκτέλεσή τους. Οι RedBlue αλγόριθμοι είναι προσαρμοστικοί και χρησιμοποιούν LL/SC (ή CAS) βασικά αντικείμενα, ενώ οι Sim αλγόριθμοι είναι απλούστεροι αλγόριθμοι που στην πράξη επιτυγχάνουν πολύ υψηλές επιδόσεις, αλλά χρησιμοποιούν Add βασικά αντικείμενα.

Σε αυτή τη διατριβή μελετήθηκε σε βάθος η συνεργατική τεχνική με στόχο την ανάπτυξη εμποδιστικών (blocking) αλγορίθμων συγχρονισμού με βελτιωμένη απόδοση και με χαρακτηριστικά δικαιότερης εξυπηρέτησης. Αναπτύχθηκαν δύο νέοι εμποδιστικοί αλγόριθ-

μοι συγχρονισμού που ανήκουν στην οικογένεια Synch. Ο πρώτος ονομάζεται CC-Synch και είναι κατάλληλος για μηχανές που υποστηρίζουν συνεπείς κρυφές μνήμες (coherent NUMA machines), ενώ ο δεύτερος ονομάζεται DSM-Synch και είναι κατάλληλος για πολυεπεξεργαστές χωρίς κρυφές μνήμες (cache-less NUMA machines). Σε αντίθεση με παλαιότερους εμποδιστικούς συνεργατικούς αλγορίθμους, οι παραπάνω αλγόριθμοι (1) προσφέρουν άνω όρια στον αριθμό των απομακρυσμένων αναφορών στη μνήμη, (2) προσφέρουν περισσότερη δικαιοσύνη κατά την προσπέλαση στο κοινόχρηστο αντικείμενο, και (3) χρησιμοποιούν απλούστερα βασικά αντικείμενα. Ο CC-Synch και ο DSM-Synch επιτυγχάνουν καλύτερη απόδοση από τον P-Sim, αλλά και όλους τους παλαιότερους αλγόριθμους συγχρονισμού.

Πολλά πολυπύρηνα συστήματα οργανώνουν τα επεξεργαστικά στοιχεία σε ομάδες και παρέχουν γρήγορη επικοινωνία μεταξύ των επεξεργαστικών στοιχείων που βρίσκονται στην ίδια ομάδα, ενώ παρέχουν αργή επικοινωνία μεταξύ των επεξεργαστικών στοιχείων διαφορετικών ομάδων. Σε αυτή τη διατριβή παρουσιάζεται μια ιεραρχική έκδοση του CC-Synch που ονομάζεται Η-Synch. Ο H-Synch εκμεταλλεύεται την ιεραρχική φύση της επικοινωνίας τέτοιων συστημάτων και η πειραματική του μελέτη έδειξε ότι ξεπερνά κατά πολύ σε απόδοση όλες τους παλαιότερους ιεραρχικούς και μη αλγόριθμους συγχρονισμού.

Σε αυτή τη διατριβή παρουσιάζονται υλοποιήσεις διαμοιραζόμενων ουρών και στοιβών πολύ υψηλών επιδόσεων που βασίζονται στους P-Sim, CC-Synch, DSM-Synch και H-Synch. Ειδικότερα, οι υλοποιήσεις SimStack και SimQueue που βασίζονται στον P-Sim ικανοποιούν τη συνθήκη τερματισμού ελεύθερη-αναμονής, ενώ εκείνες που βασίζονται στους CC-Synch, DSM-Synch και H-Synch είναι εμποδιστικές αλλά επιτυγχάνουν καλύτερες επιδόσεις από τον SimStack και SimQueue αλλά και όλες τις παλαιότερες υλοποιήσεις. Οι SimStack και SimQueue είναι οι πρώτες υλοποιήσεις κοινόχρηστων στοιβών και ουρών που πληρούν την ιδιότητα ελεύθερη-αναμονής και ταυτόχρονα επιτυγχάνουν υψηλή απόδοση.

Τα ερευνητικά αποτελέσματα αυτής της διατριβής έχουν παρουσιασθεί στα διεθνή συνέδρια/περιοδικά: ACM PPoPP 2012, ACM SPAA 2011, DISC 2009 και Theory of Computing Systems Special Issue on SPAA 2011.

### Chapter 1

#### Introduction

The last decade, the computer industry has made a significant turn towards developing multicore systems which nowadays, are used in any computing device (from smartphones to large scale multiprocessor machines). A wide variety of low cost commercial computing devices are equipped with processors containing a dozen or more processing cores. Even smartphones are equipped with multicore processors. In all of these devices, increased performance can be achieved by exploiting parallelism; thus, harnessing the difficulty of concurrent programming is currently very important.

Multicore systems are typical examples of distributed systems. A distributed system consists of a set of computing entities (threads), which have the ability to communicate. Distributed systems are distinguished in two main types depending on how the threads communicate. The first type consists of systems where threads communicate through a shared memory (shared memory systems), while the second type consists of systems that their threads communicate by exchanging messages (message passing systems). In recent years, a lot of research is conducted in shared memory systems due to the proliferation of the multicore systems. A multicore system is usually a shared memory system, since it consists of many tightly connected processing cores that communicate through shared memory.

Several applications that could be parallelized contain parts whose parallelization requires significant synchronization and coordination. Amdhal's law [9] implies that failing

in parallelizing these parts may result in a significant limitation on the speed-up that could be achieved. However, these parts usually require accesses to shared data and thus, parallelizing them demands the design of low-overhead synchronization mechanisms; without such efficient mechanisms the synchronization cost may overshadow any performance gain that could result from the parallelization of these parts.

In a shared memory system, threads use shared atomic objects (or briefly atomic objects) as main communication mechanism. Every atomic object stores some information, which is accessible to system's threads via atomic operations. Intuitively, an atomic operation is an operation that seems to be executed instantly at some point in time. Some objects, called base objects, are provided by the hardware and therefore the hardware guarantees that the supported operations are executed atomically.

The most common type of base objects are the Read-Write ones. A Read-Write base object supports two operations for accessing and modifying the stored data: a) Read(O), which returns the stored data of O without modifying it, and b) Write(O, v), which stores value v in O and returns an acknowledgment.

Other types of base objects are CAS, LL/SC, Add, Swap, etc. Specifically, a CAS base object O supports two operations: a) Read(O) that returns the stored value in O without modifying it and b) CAS(O,  $v_{old}$ ,  $v_{new}$ ). CAS(O,  $v_{old}$ ,  $v_{new}$ ) compares the current value of O with  $v_{old}$  and if they are equal it stores the value  $v_{new}$  in O and returns true. Otherwise, the contents of O remain unchanged and false is returned. An Add object supports, in addition to Read, the operation Add(O, x) that atomically adds some (positive or negative) value x to object O. A Swap object O supports in addition to Read, the operation Swap(O, v) which (atomically) writes in O the value v and returns the previous value of O. An LL/SC object O supports the atomic operations a) LL(O) which returns the current value of O, and b) SC(O, v) whose execution by a thread  $p_i$  must follow the execution of LL(O) by  $p_i$  and changes the value of O to v if no other SC (by some other thread) has changed the value of O since the execution of  $p_i$ 's latest LL on O. If the value of O changes to v by SC(O, v), true is returned; otherwise, the value of O does not change and false is returned.

Apparently, common base objects as those described above offer very simple operations for accessing stored data. The design of more complex atomic objects significantly simplifies the parallel programming of most modern applications. Thus, the design and implementation of such complex objects in software using simpler objects provided by the hardware is of high importance.

Any atomic object can be easily implemented using locks. A thread that wishes to perform an operation to the shared object, acquires the lock that is associated to the shared object, executes the sequential code of the operation and releases the lock. This methodology has been widely used in several real-world applications systems (e.g. data base applications, etc). However, this technique has a serious drawback; a thread may fail (i.e. stops its execution due to a software or hardware failure) while holding the lock leading the system to a total failure. Properties that guarantee system's progress are desirable, since it is very important for a system to be fault tolerant. A property that guarantees high tolerance in thread failures is wait-freedom [12, 16]. Wait-freedom ensures that each thread finishes the execution of the code block it wants to execute within a finite number of its own steps independently of the speed or the state of the other threads.

Atomic objects are arguably useful; however they are practical only in the case that they are implemented efficiently. From a theory perspective, the main complexity measures are the step complexity of an implementation, and the number and size of the base objects it employs. The *step complexity* of an operation is the maximum number of shared memory accesses that any thread executes in order to complete the operation. Some desirable properties when designing atomic objects in software are the following:

- The step complexity of every operation of the object should be as low as possible.

- The used base objects should support as fewer complex operations as possible.

- The needed base objects should have size equivalent to the size of hardware base objects (usually less or equal to 128 bits).

- The implementation should be fault tolerant, thus wait-freedom property should be satisfied.

A universal synchronization algorithm is a generic mechanism to implement any shared object; it supports an operation, called APPLYOP, that takes as a parameter the sequential implementation of any operation of the simulated object, and simulates its execution in a concurrent environment. A universal algorithm provides the implementation of any shared

object for free. So, if efficient implementations of universal algorithms are provided then the programming effort is highly reduced and high performance is achieved.

In the first part of this dissertation, a family of wait-free universal synchronization algorithms, called RedBlue, is presented. In shared memory systems it is often the case that the total number of threads n taking part in a computation is much larger than the actual number of threads that concurrently access the shared object. For this reason, a flurry of research [2, 3, 13, 14, 38] has been devoted to the design of adaptive algorithms whose time complexity depends on k, the maximum number of threads that concurrently access the shared object. All RedBlue algorithms are adaptive.

All RedBlue algorithms use two perfect binary trees of  $\lceil \log_2 n \rceil + 1$  levels each. The first tree (red tree) is employed for the estimation of any encountered contention, while the second tree (blue tree) is used for the synchronization with other threads when applying an operation. In each of these trees, a thread is assigned a leaf node (and therefore also a path from this leaf to the root node, or vice versa). A thread that wants to apply an operation to the simulated object, traverses first its path in the red tree from the root downwards looking for an unoccupied node in this path. Once it manages to occupy such a node, it starts traversing the blue tree upwards from the isomorphic blue node to the occupied red node, transferring information about its operation (as well as about other active operations) towards the tree's root. In this way, each operation traverses at most  $O(\min\{k, \log n\})$  nodes in each of the two trees. Once information about the operation reaches the root, the operation is applied to the simulated object.

The first algorithm of the RedBlue family, which is called F-RedBlue, has time complexity  $O(\min\{k, \log n\})$  which is better than any previously presented algorithm using LL/SC and read-write base objects. However, F-RedBlue uses big LL/SC base objects; thus it is mainly of theoretical interest. A lower bound of  $\Omega(\log n)$  on the time complexity of wait-free universal synchronizations algorithms that use LL/SC base objects is presented in [42]. It holds even if an infinite number of unbounded-size base objects is employed. Therefore, F-RedBlue is optimal in terms of time complexity.

The second algorithm (S-RedBlue) of the RedBlue family is a slightly modified version of F-RedBlue that uses smaller base objects and it is therefore practical in many cases. S-RedBlue uses O(n) LL/SC base objects, one for each of the trees' nodes and n+1 singlewriter base objects per thread. Each base object of the red tree has size  $\lceil \log_2 n \rceil + 1$ . Each

base object of the blue tree stores n bits, one for each thread. One of the base objects (the base object corresponding to the blue root) is big. This base object is implemented by single-word LL/SC objects using the technique presented in [44]. In current systems where base objects of 128 bits are available, S-RedBlue works with single-word LL/SC objects for up to 128 threads. In fact, even if n/128 = c > 1, where c is any constant, the algorithm can be implemented by single-word LL/SC base objects with the same time complexity (increased by a constant factor) using the implementation of multi-word LL/SC from single-word LL/SC of [44].

Most of the universal algorithms presented in the past, as well as F-RedBlue and S-RedBlue, copy the entire state of the object each time an update is to be performed on it by some thread. This is not practical for large objects whose states may require a large amount of storage to maintain. Anderson and Moir [11] presented a lock-free and a wait-free synchronization algorithm that is practical for large objects. Their algorithms assume that the object state is represented as a continuous array which requires B data blocks of size S each for its storage. Each operation can modify at most T blocks and each thread can help at most  $M \geq 2T$  other threads. We combine some of the techniques introduced in [11] with the techniques employed by the RedBlue algorithms in order to design two simple wait-free synchronization algorithms which have the nice properties of the constructions in [11] while achieving better time complexity and being adaptive. The time complexity of the first algorithm is better than the synchronization algorithm presented in [11] but it does not assume an upper bound on the number of threads a thread may help as the wait-free construction in [11] does. BLS-RedBlue exhibits all the properties of the wait-free construction in [11] and still achieves better time complexity. In particular, its time complexity is similar to the time complexity of the wait-free algorithm in [11] but with k replacing n and thus the algorithm is adaptive. The space complexity of the algorithm is the same as that of the wait-free algorithm in [11]. RedBlue algorithms are much simpler than the constructions presented in [11], and they improve on time complexity upon these algorithms. Table 1.1 provides the exact time complexities and the space overheads of all of the algorithms presented in this dissertation.

In the Sim family of synchronization algorithms, we aim at (1) getting better time complexity by using base objects other than LL/SC and read-write (i.e. Swap, Add, etc) and (2) competing in terms of performance with the state of the art synchronization algorithms

| Algorithm                  | Base objects  | Progress property | Published in |  |

|----------------------------|---------------|-------------------|--------------|--|

| Synchronization Algorithms |               |                   |              |  |

| F-RedBlue                  | CAS, rw       | wait-free         | DISC '09     |  |

| S-RedBlue                  | CAS, rw       | wait-free         | DISC '09     |  |

| LS-RedBlue                 | CAS, rw       | wait-free         | DISC '09     |  |

| BLS-RedBlue                | CAS, rw       | wait-free         | DISC '09     |  |

| Sim                        | Add, CAS, rw  | wait-free         | SPAA '11     |  |

| P-Sim                      | Add, CAS, rw  | wait-free         | SPAA '11     |  |

| L-Sim                      | Add, CAS, rw  | wait-free         | unpublished  |  |

| CC-Synch                   | Swap, rw      | blocking          | PPoPP '12    |  |

| DSM-Synch                  | Swap, CAS, rw | blocking          | PPoPP '12    |  |

| H-Synch                    | Swap, rw      | blocking          | PPoPP '12    |  |

| Shared Stacks              |               |                   |              |  |

| SimStack                   | Add, CAS, rw  | wait-free         | SPAA '11     |  |

| CC-Stack                   | Swap, rw      | blocking          | PPoPP '12    |  |

| DSM-Stack                  | Swap, CAS, rw | blocking          | PPoPP '12    |  |

| H-Stack                    | Swap, rw      | blocking          | PPoPP '12    |  |

| Shared Queues              |               |                   |              |  |

| SimQueue                   | Add, CAS, rw  | wait-free         | SPAA '11     |  |

| CC-Queue                   | Swap, rw      | blocking          | PPoPP '12    |  |

| DSM-Queue                  | Swap, CAS, rw | blocking          | PPoPP '12    |  |

| H-Queue                    | Swap, rw      | blocking          | PPoPP '12    |  |

Table 1.1: Algorithms and their properties proposed in this dissertation.

(i.e. high performance spin-locks, etc), while having the nice theoretical properties that RedBlue algorithms have. The family of Sim synchronization algorithms achieve these goals.

The Sim synchronization algorithm follows the simple idea presented by Herlihy in [37]: a thread p starts by recording the request that it wants to execute in a shared struct that it owns. This struct additionally contains a toggle bit. A set of toggle bits, one for each thread, are also stored as part of the simulated state. Based on the values of the toggle bits, p finds out which other requests are active and serves them by executing their code on a local copy of the simulated state. Finally, p tries to change a shared reference, stored in an LL/SC object, to point to this local struct. Process p may have to apply these steps twice to ensure that its request has been served. An array containing p response values is also stored as part of the simulated state. Once p ensures that its request has been served, it finds its response value in the LL/SC object.

We start with Sim, a simplified version of this technique that allows us to derive some theoretical results. In Sim, the announcement of the requests and the discovery of the active requests by each thread have been abstracted using a collect object. A collect object consists of n components  $A_1, ..., A_n$ , one for each thread, where each component stores a value from some set and supports two operations  $\operatorname{UPDATE}(v)$  and  $\operatorname{COLLECT}$ . When executed by thread  $p_i$ ,  $1 \leq i \leq n$ ,  $\operatorname{UPDATE}(v)$  stores the value v in  $A_i$ ;  $\operatorname{COLLECT}$  returns a vector of n values, one for each component. It is remarkable that a collect object is not atomic (see Section 3 for a description of the correctness condition that needs to be ensured by an implementation of a collect object). A snapshot object is an atomic version of a collect object.

We describe simple implementations of collect and snapshot objects using a single atomic Add (or XOR) object. An Add (XOR) object supports the operation Add (XOR) in addition to Read; Add(O, x) adds some (positive or negative) value x to object O (XOR(O, x) computes O XOR v and stores it into O). These implementations exhibit constant step complexity (under the standard theoretical model of shared memory computation where even if the size of the Add object is large, an Add can be executed atomically as a single step). Using these simple implementations, one could get improved performance for several previously presented algorithms [7, 15, 40, 57].

By plugging in to Sim the implementation of collect discussed above, the step complexity of Sim becomes constant as well. Jayanti [42] has proved a lower bound of  $\Omega(\log n)$  on the step complexity of any oblivious universal synchronization algorithm using LL/SC objects; an *oblivious* universal synchronization algorithm does not exploit the semantics of the object being simulated. This lower bound holds even if the size of the base objects used by the universal synchronization algorithm is unbounded. One of the open problems mentioned in [42] is the following: "If shared-memory supports all of Read, Write, LL/SC, Swap, CAS, Move, Fetch&Add, would the  $\Omega(\log n)$  lower bound still hold?" Sim has constant step complexity and it uses a single Add (or XOR) object in addition to an LL/SC object, thus proving that the lower bound in [42] can be beaten if we use just a single Add (or XOR) object in addition to an LL/SC object. So, an  $\Omega(\log n)$  lower bound can be derived for the step complexity of any implementation of an Add, XOR, collect, or a snapshot object, from LL/SC objects.

Sim is an efficient wait-free implementation of the well-known combining technique [29, 34, 37, 52, 54, 56, 60]. Most of the previous implementations of this technique, including the algorithm presented in [52] (which we will call OyamaAlg from now on) and flat-combining [34], employ locks and therefore they are *blocking* (i.e. threads may have to wait for actions performed by other threads in order to make progress). Specifically, in those algorithms, a thread, called the *combiner*, holding a coarse-grain lock, serves, in addition to its own request, active requests announced by other threads while they are waiting by performing local spinning (and possibly periodical checking of the lock status).

We present a practical version of Sim, called P-Sim, which we have implemented and experimentally tested on a real shared memory machine. We provide a detailed experimental analysis illustrating that P-Sim is highly-efficient in practice. Specifically, our experiments show that P-Sim outperforms several state-of-the-art synchronization algorithms, both lock-based (like local spinning) and lock-free (Figures 5.2-5.12). Moreover, the performance of P-Sim is as good as that of the best-known implementations [34, 52] of the combining technique, and in some cases even better than them. More specifically, we experimentally compare P-Sim with OyamaAlg [52], flat-combining [34], CLH spin locks [23, 47], and a simple lock free algorithm. Our experiments (Figure 5.2) show that P-Sim outperforms all these algorithms in several cases. Besides that, P-Sim is wait-free whereas all other algorithms ensure only weaker progress properties. P-Sim proves that the common belief that ensuring wait-freedom is too expensive to be practical is in many cases wrong.

We have used P-Sim to design new highly-efficient wait-free implementations of common concurrent data structures like queues and stacks. We experimentally prove that our stack implementation, called SimStack, outperforms most well-known previous shared stack algorithms, like the lock-free stack implementation of Treiber [58], the elimination back-off stack [35], a stack implementation based on a CLH spin lock [23, 47], and a linked stack implementation based on flat-combining [34]. Similarly, our queue implementation, called SimQueue significantly outperforms the following previous queue implementations: a lock-based algorithm [50] which uses two CLH locks [23, 47], the lock-free algorithm presented in [50], and the implementation using flat-combining provided by Hendler et. al [34].

In this dissertation, a further investigation of the combining technique is provided aiming at discovering where its real performance power resides, understanding the performance implications of using different primitives when implementing it, and investigating whether and how ensuring some desired properties (e.g., fairness in serving requests) would impact performance. We do so by presenting two new blocking implementations of this technique. The first, called CC-Synch, is suitable for cache coherent (CC) shared memory systems where accesses to shared objects are performed via cached copies of them; an access to a shared object is a remote memory reference (RMR) if the cached copy of this object is invalid, so the access causes a cache miss\*. The vast majority of modern parallel architectures follow the CC shared memory model. The second implementation, called DSM-Synch, is better suited for the cache-less NUMA shared memory systems, where a part of the shared memory is associated with each processor; so, each shared object is allocated (and resides) in the part of the shared memory that is associated to a specific processor. Processors do not have access to local caches, so a thread p performs a remote memory reference (RMR) if it accesses a shared object residing in the shared memory part of some processor other than that where p is being executed. Since an RMR is significantly more costly than a local memory reference [49], it is highly desirable to design algorithms that perform as few RMRs as possible; CC-Synch and DSM-Synch perform a bounded number of RMRs.

CC-Synch and DSM-Synch use a single FIFO queue to both implement the lock and store the active synchronization requests. Therefore, the synchronization needed for implementing the list of active requests comes for free. Specifically, each newly activated thread adds a node to the tail of the queue to announce its request and participate to the implementation of the lock. Thus, each active thread is assigned one of the nodes of the queue. The active thread q that owns the first node of the queue becomes the combiner and undertakes the responsibility of applying some (or all) of the requests listed in the queue. Each active thread whose node is not first in the queue performs local spinning.

The experimental analysis (Section 6.4) reveals that the use of a highly-efficient queuelike lock which, in addition to its low synchronization overhead, provides the implementation of the list of announced requests for free, significantly reduces the synchronization required to implement the combining technique. Moreover, the new implementations are simpler to program than previous combining-based synchronization approaches [34, 52].

<sup>\*</sup> Once the cache miss is served and as long as the data item is not updated by threads that are being executed on other processors, future accesses to the data item by threads that are being executed on this processor are local.

These result in a performance benefit in comparison to P-Sim as well as to any other algorithm provided in the past. Additionally, the new implementations exhibit several nice properties, not ensured by previous blocking combining implementations [34, 52]. First, they provide stronger fairness guarantees in serving the requests. Second, they provide bounds on the number of remote memory references that are executed. Specifically, in CC-Synch, the combiner thread performs O(h+t) RMRs, where h is an upper bound on the number of synchronization requests that the combiner may serve, and t is the size of the shared data that should be accessed in order to execute these h requests; we remark that h is a parameter that can be determined by the user and it can be chosen to be constant. The combiner in DSM-Synch performs O(dh) RMRs, where d is the average number of RMRs required to serve a single request. In both algorithms, all threads, other than the combiner, perform local spinning and cause only a constant number of RMRs. Thus, the amortized number of performed RMRs is O(d). Moreover, no thread may ever starve. Finally, the new implementations do not employ any form of backoff and they need minimal tuning to achieve the best performance.

CC-Synch uses a Swap object in addition to Read-Write base objects. DSM-Synch uses an object that supports CAS and Swap in addition to Read-Write base objects; a CAS(O, u, v) (atomically) checks if the current value of O is u and if this is so, it changes the value of O to v and returns true, otherwise the value of O remains unchanged and false is returned. CC-Synch and DSM-Synch use just one primitive stronger than Read-Write base objects and in CC-Synch this is a Swap object which is weaker than CAS. In CC-Synch, each thread maintains a single node to insert in the list, and therefore the total space overhead of CC-Synch is O(n), where n is the number of threads; this is no more than that of previous combining-based synchronization approaches. The total space overhead for DSM-Synch is also O(n).

We experimentally compare CC-Synch and DSM-Synch with several state-of-the-art synchronization approaches, like P-Sim, flat-combining [34], CLH spin locks [23, 47], and a simple lock free algorithm. The experiments (Figures 6.1-6.10) show that CC-Synch outperforms all these approaches in most cases. DSM-Synch outperforms all algorithms other than CC-Synch. DSM-Synch has the advantage over CC-Synch that it is designed to be efficient even in machines that support the DSM model; so, it can be executed efficiently by architecture unaware applications.

The experimental analysis reveals that the number of cache misses incurred per request is smaller in the new implementations than in previous algorithms and the same is true for the cycles invested in memory stalls. Based on experiments, we conclude that the algorithm of repeatedly performing CAS until it succeeds, even if it comes together with an appropriately-tuned back-off scheme, causes more cache misses and more branch mispredictions than employing Swap or other non-comparison primitives. Experiments also show that the average number of requests served by a combiner in CC-Synch and DSM-Synch is larger than in other algorithms, so the synchronization overhead paid to serve an amount of requests in these implementations is closer to the ideal than in previous approaches. So, the achieved combining degree has a significant impact on the performance of combining implementations.

We used CC-Synch and DSM-Synch to implement shared stacks and queues (Section 6.5). The stack implementation (CC-Stack) based on CC-Synch, outperforms all state-of-the-art shared stack implementations like SimStack, the linked stack implementation based on flat-combining [34] where elimination has also been applied [35], and the stack implementation based on CLH spin locks [23, 47]. The stack implementation (DSM-Stack) based on DSM-Synch, outperforms all implementations other than CC-Stack. We also use CC-Synch and DSM-Synch to get two highly efficient shared queue implementations, called CC-Queue and DSM-Queue. More specifically, these implementations are derived by simply replacing the ordinary locks in the two-locks queue implementation presented by Michael and Scott in [50] with two instances of either CC-Synch or DSM-Synch. These implementations were experimentally compared to SimQueue, the two-locks implementation [50], and the queue implementation based on flat-combining presented in [34]. CC-Queue performs up to 2.5 times faster than the queue implementation of [34] and outperforms SimQueue by a factor of up to 1.5.

For modern multi-core systems that organize the cores into clusters and provide fast communication (via shared caches) to the threads running in the same cluster and much slower communication across clusters, we present an hierarchical version of CC-Synch, called H-Synch, which exploits the hierarchical communication nature of such systems to achieve better performance. Experiments show that in such systems, H-Synch significantly outperforms CC-Synch and DSM-Synch as well as the state-of-the-art flat-combining NUMA locks recently presented by Dice et. al in [24]. H-Synch is used to design highly

efficient implementations of stacks and queues for such machines. These implementations outperform by far, in such machines, CC-Stack, DSM-Stack, CC-Queue and DSM-Queue, respectively, as well as all other concurrent stack and queue implementations with which these implementations have been compared.

Many hardware manufactures have been influenced by the universality result [36], and they have equipped their machines with strong atomic primitives (like CAS and LL/SC). Sim shows that machines that additionally support Add instructions, have important performance advantages, and can ensure wait-freedom. CC-Synch and DSM-Synch show that machines that support Swap objects have even better performance benefits. We believe that the results of this dissertation provide some motivation for seeing primitives such as Add provided in the instruction set of more architectures in the future.

Note that CC-Synch, similarly to Sim and flat-combining [34], cannot be trivially applied in an efficient way for designing data structures such as search trees, where m lookups can be executed in parallel performing just a logarithmic number of shared memory accesses each. In such cases, it is expected that CC-Synch will perform well, only if several instances of it are employed. It is an interesting open problem to find efficient ways to synchronize these instances. It is also not obvious how to use the combining technique to implement data structures, like shared linked lists, if several instances of the combining implementation should be employed to achieve good speed-up.

The synchronization algorithms of the RedBlue synchronization algorithms have been presented in DISC '09 [27], synchronization algorithms based on Sim have been presented in SPAA 2011 [28] and an extended version will appear to Theory of Computing Systems Special Issue on SPAA 2011, while the Synch synchronization algorithms are presented in PPoPP [29].

This dissertation is organized as follows. The related work is discussed in Chapter 2. The model of the system is described in Chapter 3. In Chapter 4, the family of RedBlue algorithms is presented. The family of Sim algorithms is provided in Chapter 5. Finally, the family of Synch algorithms is presented in Chapter 6.

### Chapter 2

### Related Work

In [36], Herlihy provides the first wait-free universal synchronization algorithm using Read-Write base objects and consensus objects. This universal algorithm can be used to simulate any other shared object in a system of n threads. Herlihy's algorithm uses  $O(n^2)$  Read-Write base objects and  $O(n^2)$  consensus objects of size s, where s is the size of the state of the simulated object. The consensus objects can be easily implemented by using CAS or LL/SC base objects [36]. The step complexity of Herlihy's synchronization algorithm is O(n).

Afek, Dauber and Touitou [4] have presented algorithm GroupUpdate which also uses a tree technique to keep track of the list of active threads. They then combine this tree construction with Herlihy's universal algorithm [36, 37] to get a universal construction with time complexity  $O(k \log k + W + kD)$ , where W is the size (in words) of the simulated object state and D is the time required for performing a sequential request on it. F-RedBlue retains the basic structure of GroupUpdate but achieves better time complexity  $(O(\min\{k, \log n\}))$  by employing a faster mechanism to discover the encountered contention and by using large LL/SC base objects. S-RedBlue addresses the problem of using large base objects still achieving better time complexity than GroupUpdate.

Although the first of the RedBlue algorithms shares a lot of ideas with GroupUpdate, it also exhibits several differences: (1) it employs two complete binary trees each of which has one more level than the single tree employed by GroupUpdate; in each of these trees, each

thread is assigned its own leaf node which identifies a unique path (from the root to this leaf) in the tree for the thread; (2) threads traverse the red tree first in order to occupy a node and this procedure is faster than a corresponding procedure in GroupUpdate. More specifically, GroupUpdate performs a BFS traversal of its employed tree in order for a thread to occupy a node of the tree, while each thread in any of the RedBlue algorithms always traverses appropriate portions of its unique path. This results in reduced time complexity for some of the RedBlue algorithms.

Afek, Dauber and Touitou [4] present a technique that employs indirection to reduce the size of the base objects used by GroupUpdate (each tree base object stores a thread id and a pointer to a list of ids of currently active threads). A similar technique can be applied to the RedBlue algorithms in case n is too large to have n bits stored in a constant number of LL/SC base objects. The resulting algorithms will have just a pointer stored in each of the blue nodes (thus using smaller base objects than GroupUpdate which additionally stores a thread id in each of its LL/SC base objects). However, employing this technique would cause an increase to the step complexity of our algorithms by an  $O(k \log n)$  additive term.

Afek, Dauber and Touitou present in [4] a second universal construction, called IndividualUpdate, that has time complexity O(k(W+D)). IndividualUpdate stores sequence numbers in base objects and therefore it requires unbounded size base objects or base objects that support the VL request in addition to LL and SC. The first two RedBlue algorithms achieve better time complexity than IndividualUpdate. Some of our algorithms use single-word base objects (however, they also employ LL/VL/SC objects).

Afek, Dauber and Touitou [4] discuss a method similar to that presented in [17] to avoid copying the entire object's state in IndividualUpdate. The resulting algorithm has time complexity  $O(kD \log D)$ . The work of Anderson and Moir on universal constructions for large objects [11] follows this work. Our last two algorithms improve in terms of time complexity upon the constructions presented in [11]. They achieve this using single-word base objects (and the last algorithm with the same space complexity as the wait-free construction in [11]).

Jayanti [43] presented f-arrays, a generalized version of a snapshot object which allows the execution of any aggregation function f on the m elements of an array of m memory cells that can be updated concurrently. As F-RedBlue, f-arrays has time com-

| Algorithm                                                           | Primitives                        | Shared Memory Accesses                                 | Required Space        |  |  |

|---------------------------------------------------------------------|-----------------------------------|--------------------------------------------------------|-----------------------|--|--|

| Wait-free synchronization algorithms presented in this dissertation |                                   |                                                        |                       |  |  |

| F-RedBlue                                                           | LL/SC                             | $O(\min\{k, \log n\})$                                 | $O(n^2+s)$            |  |  |

| S-RedBlue                                                           | LL/VL/SC, r/w regs                | O(k+s)                                                 | $O(n^2 + ns)$         |  |  |

| LS-RedBlue                                                          | LL/VL/SC, r/w regs                | O(B + k(w + TL))                                       | $O(n^2 + n(B + kTL))$ |  |  |

| BLS-RedBlue                                                         | LL/VL/SC, r/w regs                | $O((k/\min\{k, M/T\}) (B + ML + k + \min\{k, M/T\}w))$ | $O(n^2 + n(B + ML))$  |  |  |

| Sim                                                                 | LL/SC or CAS, FAD                 | O(1)                                                   | O(n+s)                |  |  |

| P-Sim                                                               | LL/SC or CAS, Fetch&Add           | O(n+s)                                                 | $O(n^2 + ns)$         |  |  |

| Related Work                                                        |                                   |                                                        |                       |  |  |

| Herlihy [36]                                                        | consensus objects, r/w regs       | O(n)                                                   | $O(n^3s)$             |  |  |

| Herlihy [37]                                                        | LL/VL/SCor CAS, r/w regs          | O(n+s)                                                 | O(ns)                 |  |  |

| GroupUpdate [4]                                                     | LL/SC r/w regs, consensus objects | $O(\min\{n, k \log k\})$                               | $O(n^2 s \log n)$     |  |  |

| IndividualUpdate [4]                                                | LL/VL/SC                          | $O(kw \log w)$                                         | O(nw+s)               |  |  |

| Anderson & Moir [10]                                                | LL/VL/SC                          | $O((n/\min\{k, M/T\}) (B + ML + nw))$                  | $O(n^2 + n(B + ML))$  |  |  |

| Chuong, et. al [20]                                                 | CAS, r/w regs                     | O(nw)                                                  | O(n+s)                |  |  |

Table 2.1: Wait-free universal algorithms and their complexities.

plexity  $O(\min\{k, \log n\})$ ; the algorithm uses a tree structure similar to that employed by GroupUpdate and our algorithm. F-RedBlue is universal, thus achieving wider functionality than f-arrays. Constructions for other restricted classes of objects with polylogarithmic complexity are presented in [19].

Afek et al. [5, 6] and Anderson and Moir [10] have presented universal algorithms for multi-object requests that support access to multiple objects atomically. The main difficulty encountered under this setting is to ensure good parallelism in cases where different requests perform updates in different parts of the object's state. In Table 2.1, a comparison between the wait-free algorithms proposed in this dissertation and previous work is displayed. Notice that w is the maximum number of different memory words accessed by an operation on the sequential data structure. In [10, 27], B is the number of blocks, each of size L, required to store the object's state, and each thread is allowed to modify at most T blocks and help at most M/T other threads, where  $M \geq 2T$  is some integer.

P-Sim uses an efficient implementation of the Add-based collect object. This allows a thread to read only the announcement records of those requests that are active improving upon the technique described in [37] where threads read all n such records. Furthermore, in P-Sim each thread uses its own pool of structs to store the simulated state. In the recycling technique of [37] threads share the same pool which leads to a significantly higher

number of cache misses. P-Sim validates not only whether the copied state is consistent (as does the validation mechanism in [37]), but also if the reference to the shared state has changed in the meantime. If the validation fails, P-Sim avoids performing unnecessary work. Moreover, P-Sim uses a simple backoff scheme to guarantee that a thread executing a request will help a large number of other active threads; in [37], the employed backoff scheme aims at reducing the contention in updating the LL/SC object.